La Interfaz Extensible Avanzada ( AXI ) es un protocolo de bus de comunicación en chip y forma parte de la especificación de Arquitectura de Bus de Microcontrolador Avanzado (AMBA). [1] [2] AXI se introdujo en 2003 con la especificación AMBA3. En 2010, una nueva revisión de AMBA, AMBA4, definió los protocolos AXI4, AXI4-Lite y AXI4-Stream . AXI está libre de regalías y su especificación está disponible gratuitamente en ARM .

AMBA AXI especifica muchas señales opcionales , que pueden incluirse dependiendo de los requisitos específicos del diseño, [3] haciendo de AXI un bus versátil para numerosas aplicaciones.

Si bien la comunicación a través de un bus AXI es entre un único iniciador y un único objetivo, la especificación incluye descripciones detalladas y señales para incluir interconexiones N:M, capaces de extender el bus a topologías con múltiples iniciadores y objetivos. [4]

Xilinx y muchos de sus socios han adoptado AMBA AXI4, AXI4-Lite y AXI4-Stream como bus de comunicación principal en sus productos. [5] [6]

Los identificadores de subproceso permiten que un único puerto iniciador admita varios subprocesos, donde cada subproceso tiene acceso en orden al espacio de direcciones AXI; sin embargo, cada identificador de subproceso iniciado desde un único puerto iniciador puede completarse fuera de orden con respecto a los demás. Por ejemplo, en el caso en que un identificador de subproceso esté bloqueado por un periférico lento, otro identificador de subproceso puede continuar independientemente del orden del primer identificador de subproceso. Otro ejemplo, a un subproceso de una CPU se le puede asignar un identificador de subproceso para un acceso de memoria de puerto iniciador particular, como read addr1, write addr1, read addr1, y esta secuencia se completará en orden porque cada transacción tiene el mismo identificador de subproceso de puerto iniciador. Otro subproceso que se ejecuta en la CPU puede tener otro identificador de subproceso de puerto iniciador asignado a él, y su acceso a memoria también estará en orden, pero puede estar entremezclado con las transacciones del primer identificador de subproceso.

Los identificadores de subprocesos en un puerto iniciador no están definidos globalmente, por lo que un conmutador AXI con varios puertos iniciadores antepondrá internamente el índice del puerto iniciador al identificador de subproceso y proporcionará este identificador de subproceso concatenado al dispositivo de destino. Luego, al regresar la transacción a su puerto iniciador de origen, este prefijo de identificador de subproceso se utilizará para ubicar el puerto iniciador y el prefijo se truncará. Es por esto que el identificador de subproceso del puerto de destino es más amplio en bits que el identificador de subproceso del puerto iniciador.

El bus AXI-Lite es un bus AXI que solo admite un único subproceso de ID por iniciador. Este bus se utiliza normalmente para un punto final que solo necesita comunicarse con un único dispositivo iniciador a la vez, por ejemplo, un periférico simple como un UART . Por el contrario, una CPU es capaz de iniciar transacciones a múltiples periféricos y espacios de direcciones a la vez, y admitirá más de un ID de subproceso en sus puertos de iniciador AXI y puertos de destino AXI. Es por eso que una CPU normalmente admitirá un bus AXI de especificación completa. Un ejemplo típico de un conmutador AXI de lado frontal incluiría un iniciador AXI de especificación completa conectado a un iniciador de CPU y varios destinos AXI-Lite conectados al conmutador AXI desde diferentes dispositivos periféricos.

(Además, el bus AXI-Lite está restringido a admitir únicamente longitudes de transacción de una sola palabra de datos por transacción).

AXI define un mecanismo básico de protocolo de enlace , compuesto por una señal xVALIDy [7] . La señal es impulsada por la fuente para informar a la entidad de destino que la carga útil en el canal es válida y se puede leer a partir de ese ciclo de reloj en adelante. De manera similar, la señal es impulsada por la entidad receptora para notificar que está preparada para recibir datos.xREADYxVALIDxREADY

Cuando las señales xVALIDy xREADYson altas en el mismo ciclo de reloj , se considera que la carga útil de datos se ha transferido y la fuente puede proporcionar una nueva carga útil de datos, manteniendo alta xVALID, o finalizar la transmisión, anulando la confirmación xVALID. Una transferencia de datos individual, es decir, un ciclo de reloj cuando tanto xVALIDy xREADYson altas, se denomina "latido".

Se definen dos reglas principales para el control de estas señales:

xREADYpara afirmarlo xVALID.xVALIDque se afirma algo, una fuente debe mantener la afirmación hasta que se produzca un apretón de manos.Gracias a este mecanismo de protocolo de enlace , tanto el origen como el destino pueden controlar el flujo de datos, limitando la velocidad si es necesario.

En la especificación AXI se describen cinco canales : [8]

Aparte de algunas reglas de ordenamiento básicas, [9] cada canal es independiente de los demás y tiene su propio par de señales xVALID/xREADY de enlace . [10]

[11]

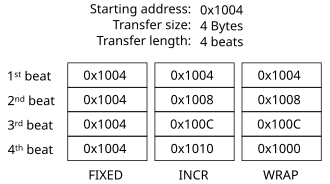

AXI es un protocolo basado en ráfagas , [12] lo que significa que pueden existir múltiples transferencias de datos (o pulsos) para una sola solicitud. Esto lo hace útil en los casos en los que es necesario transferir una gran cantidad de datos desde o hacia un patrón específico de direcciones. En AXI, las ráfagas pueden ser de tres tipos, seleccionadas por las señales ARBURST (para lecturas) o AWBURST (para escrituras): [13]

En las ráfagas FIJAS, cada latido dentro de la transferencia tiene la misma dirección. Esto es útil para el acceso repetido a la misma ubicación de memoria, como al leer o escribir un FIFO .

En cambio, en las ráfagas INCR, cada latido tiene una dirección igual a la anterior más el tamaño de transferencia. Este tipo de ráfaga se utiliza habitualmente para leer o escribir áreas de memoria secuenciales.

Las ráfagas WRAP son similares a las INCR, ya que cada transferencia tiene una dirección igual a la anterior más el tamaño de la transferencia. Sin embargo, con las ráfagas WRAP, si la dirección del latido actual alcanza el "límite de dirección superior", se restablece al "límite de Wrap":

con

Para iniciar una transacción de lectura, el iniciador debe proporcionar en el canal de dirección de lectura:

Además, las otras señales auxiliares, si están presentes, se utilizan para definir transferencias más específicas.

Después del protocolo de enlace ARVALID/ARREADY habitual, el destino debe proporcionar en el canal de lectura de datos:

más cualquier otra señal opcional. Cada latido de la respuesta del objetivo se realiza con un protocolo de enlace RVALID/RREADY y, en la última transferencia, el objetivo debe activar RLAST para informar que no habrá más latidos sin una nueva solicitud de lectura.

Para iniciar una operación de escritura, el iniciador debe proporcionar tanto la información de dirección como la de datos.

La información de la dirección se proporciona a través del canal de dirección de escritura, de manera similar a una operación de lectura:

y, si están presentes, todas las señales opcionales.

Un iniciador también debe proporcionar los datos relacionados con las direcciones especificadas en el canal de datos de escritura:

Al igual que en la ruta de lectura, en la última palabra de datos, el iniciador debe confirmar WLAST.

Una vez completadas ambas transacciones, el objetivo debe enviar de vuelta al iniciador el estado de la escritura a través del canal de respuesta de escritura, devolviendo el resultado a través de la señal BRESP.

AXI4-Lite es un subconjunto del protocolo AXI4, que proporciona una estructura similar a un registro con funciones y complejidad reducidas. [15] Las diferencias notables son:

AXI4-Lite elimina parte de las señales AXI4 pero sigue la especificación AXI4 para las restantes. Al ser un subconjunto de AXI4, las transacciones AXI4-Lite son totalmente compatibles con los dispositivos AXI4, lo que permite la interoperabilidad entre los iniciadores AXI4-Lite y los destinos AXI4 sin lógica de conversión adicional. [16]

[17]

AXI4-Stream es un protocolo de bus simplificado y liviano diseñado específicamente para aplicaciones de transmisión de datos a alta velocidad. Admite solo flujo de datos unidireccional, sin necesidad de direccionamiento ni protocolos de enlace complejos. Un AXI Stream es similar a un canal de datos de escritura AXI, con algunas diferencias importantes en la forma en que se organizan los datos:

El protocolo AXI5 Stream introduce señalización de activación y protección de señal mediante paridad.

Un solo transmisor AXI Stream puede controlar múltiples transmisiones que pueden intercalarse, pero no se permite reordenarlas.

El protocolo que utilizan muchos diseñadores de SoC en la actualidad es AXI, o Advanced eXtensible Interface, y forma parte de la especificación de la Arquitectura avanzada de bus de microcontroladores (AMBA) de Arm. Es especialmente frecuente en los dispositivos Zynq de Xilinx, ya que proporciona la interfaz entre el sistema de procesamiento y las secciones de lógica programable del chip.