El chip de interfaz periférica programable (PPI) Intel 8255 (o i8255 ) fue desarrollado y fabricado por Intel en la primera mitad de la década de 1970 para el microprocesador Intel 8080. El 8255 proporciona 24 líneas de entrada/salida paralelas con una variedad de modos operativos programables.

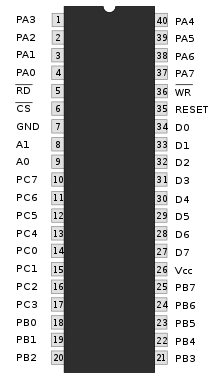

El 8255 es un miembro de la familia de chips MCS-85 , diseñado por Intel para su uso con sus microprocesadores 8085 y 8086 y sus descendientes. [1] Primero estuvo disponible en paquetes DIP de 40 pines y luego en paquetes PLCC de 44 pines . [2] Encontró una amplia aplicabilidad en sistemas de procesamiento digital y luego fue clonado por otros fabricantes. El 82C55 es una versión CMOS para mayor velocidad y menor consumo de corriente.

La funcionalidad del 8255 ahora está integrada principalmente en chips de procesamiento VLSI más grandes como una subfunción. Renesas todavía fabrica una versión CMOS del 8255 [ 3], pero se utiliza principalmente para expandir la E/S de los microcontroladores .

El 8255 tiene una función similar al PIA (Adaptador de Interfaz Periférico) Motorola 6820 de la familia Motorola 6800 , también empaquetado originalmente como DIL de 40 pines. El 8255 proporciona 24 pines de E/S con cuatro bits de dirección programables: uno para el Puerto A (7:0) (es decir, todos los pines del puerto), uno para el Puerto B (7:0), uno para el Puerto C (3:0) y uno para el Puerto C (7:4). Por el contrario, los chips Motorola y MOS proporcionan solo 16 pines de E/S más 4 pines de control, pero los chips Motorola/MOS permiten programar individualmente la dirección (entrada o salida) de todos los pines de E/S. Ambos tienen configuraciones que realizarán una cierta cantidad de intercambio automático de señales y generación de interrupciones.

Otros chips de entrada/salida de microprocesador comparables son la interfaz periférica programable 2655 de la familia Signetics 2650 , el Z80 PIO , el Western Design Center WDC 65C21 (equivalente al Motorola 6820/6821) y el MOS Technology 6522 VIA y 6526 CIA que tenían una funcionalidad adicional considerable, como temporizadores y registros de desplazamiento.

La versión de grado industrial de Intel ID8255A estaba disponible por US$17,55 en cantidades de 100 o más. [4] La versión Intel 8255A-5 disponible estaba a US$6,55 en cantidades de 100 o más. [5] La versión CMOS 82C55A disponible fue subcontratada a Oki Electronic Industry Co., Ltd. [ 6] El paquete disponible de Intel con la marca 82C55 en PLCC de 44 pines de muestreo en el cuarto trimestre de 1985. [7] En Europa del Este, se fabricaron circuitos equivalentes como KR580VV55A en la Unión Soviética y como MHB8255A por Tesla en Checoslovaquia.

El 8255 se utilizó ampliamente en muchos sistemas de microcomputadoras/microcontroladores y computadoras domésticas como la SV-328 y todos los modelos MSX . El 8255 se utilizó en la IBM-PC original , [8] PC/XT, PC/jr y clones, junto con numerosas computadoras caseras como la N8VEM .

El 8255 proporciona a una CPU o a un sistema digital acceso a E/S paralelas programables . [9] El 8255 tiene 24 pines de entrada/salida. [10] Estos se dividen en tres puertos de 8 bits (A, B, C). [11] El puerto A y el puerto B se pueden utilizar como puertos de entrada/salida de 8 bits. El puerto C se puede utilizar como un puerto de entrada/salida de 8 bits o como dos puertos de entrada/salida de 4 bits o para producir señales de protocolo de enlace para los puertos A y B.

Los tres puertos se agrupan además de la siguiente manera:

Hay ocho líneas de datos (D0–D7) disponibles (con un búfer de datos de 8 bits) para leer/escribir datos en los puertos o en el registro de control bajo el estado de RD (pin 5) y WR (pin 36), que son señales activas bajas para operaciones de lectura y escritura respectivamente. Las líneas de dirección A1 y A0 permiten acceder a un registro de datos para cada puerto o a un registro de control, como se indica a continuación :

La señal de control de selección de chip CS (pin 6) se utiliza para habilitar el chip 8255. Es una señal activa baja, es decir, cuando CS = 0, el 8255 está habilitado. La entrada RESET (pin 35) está conectada a la línea RESET del sistema como 8085, 8086, etc., de modo que cuando el sistema se reinicia, todos los puertos se inicializan como líneas de entrada. Esto se hace para evitar que el 8255 y/o cualquier periférico conectado a él se destruya debido a una falta de coincidencia en la configuración de la dirección del puerto. Como ejemplo, considere un dispositivo de entrada conectado al 8255 en el puerto A. Si a partir de la operación anterior, el puerto A se inicializa como un puerto de salida y si el 8255 no se reinicia antes de usar la configuración actual, entonces existe la posibilidad de daño del dispositivo de entrada conectado o del 8255 o de ambos, ya que tanto el 8255 como el dispositivo conectado enviarán datos.

El registro de control (o la lógica de control, o el registro de palabras de comando) es un registro de 8 bits que se utiliza para seleccionar los modos de operación y la designación de entrada/salida de los puertos. [12]

Hay dos modos operativos básicos del 8255:

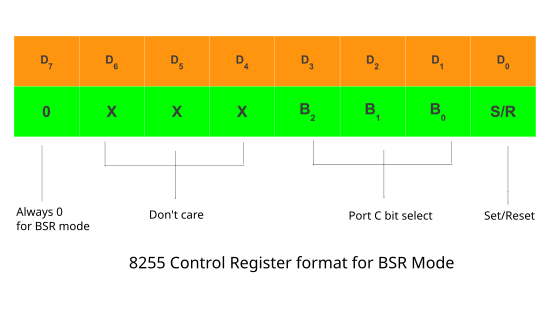

Los dos modos se seleccionan en función del valor presente en el bit D 7 del registro de palabra de control. Cuando D 7 = 1, 8255 opera en modo E/S, y cuando D 7 = 0, opera en modo BSR.

El modo de configuración/reinicio de bits (BSR) está disponible únicamente en el puerto C. Cada línea del puerto C (PC 7 - PC 0 ) se puede configurar o reiniciar escribiendo un valor adecuado en el registro de palabras de control. El modo BSR y el modo de E/S son independientes y la selección del modo BSR no afecta el funcionamiento de otros puertos en el modo de E/S. [13]

La selección del pin del puerto C se determina de la siguiente manera:

A modo de ejemplo, si se necesita configurar PC 5 , entonces en la palabra de control,

Por lo tanto, según los valores anteriores, se cargará 0B (Hex) en el Registro de palabras de control (CWR).

Este modo se selecciona cuando el bit D 7 del Registro de palabra de control es 1. Hay tres modos de E/S: [14]

Por ejemplo, si el puerto B y el puerto superior C deben inicializarse como puertos de entrada y el puerto inferior C y el puerto A como puertos de salida (todos en modo 0):

Por lo tanto, para la operación deseada, el registro de palabra de control deberá cargarse con "10001010" = 8A (hexadecimal) .

En este modo, los puertos se pueden utilizar para operaciones de E/S sencillas sin señales de enlace. El puerto A y el puerto B proporcionan una operación de E/S sencilla. Las dos mitades del puerto C se pueden utilizar juntas como un puerto adicional de 8 bits o como puertos individuales de 4 bits. Dado que las dos mitades del puerto C son independientes, se pueden utilizar de forma que una mitad se inicialice como puerto de entrada mientras que la otra mitad se inicialice como puerto de salida.

Las características de entrada/salida en el modo 0 son las siguientes:

'Enclavado' significa que los bits se colocan en un registro de almacenamiento (una matriz de flip-flops) que mantiene su salida constante incluso si las entradas cambian después de ser bloqueados.

Las salidas del 8255 están bloqueadas para retener los últimos datos escritos en ellas. Esto es necesario porque los datos solo permanecen en el bus durante un ciclo. Por lo tanto, sin bloqueo, las salidas se volverían inválidas tan pronto como finalice el ciclo de escritura.

Las entradas no están bloqueadas porque la CPU solo tiene que leer sus valores actuales y luego almacenar los datos en un registro de la CPU o en la memoria si es necesario hacer referencia a ellos en un momento posterior. Si una entrada cambia mientras se lee el puerto, el resultado puede ser indeterminado.

Cuando deseamos utilizar el puerto A o el puerto B para operaciones de entrada o salida de handshake (estroboscópico), inicializamos ese puerto en modo 1 (el puerto A y el puerto B se pueden inicializar para operar en modos diferentes, es decir, por ejemplo, el puerto A puede operar en modo 0 y el puerto B en modo 1). Algunos de los pines del puerto C funcionan como líneas de handshake.

Para el puerto B en este modo (independientemente de si actúa como puerto de entrada o puerto de salida), los pines PC0, PC1 y PC2 funcionan como líneas de enlace.

Si el puerto A se inicializa como puerto de entrada de modo 1, entonces PC3, PC4 y PC5 funcionan como señales de enlace. Los pines PC6 y PC7 están disponibles para usarse como líneas de entrada/salida.

El modo 1 que admite el protocolo de enlace tiene las siguientes características:

Señales de protocolo de entrada

Señales de protocolo de enlace de salida

En este modo, solo se puede inicializar el puerto A. El puerto A se puede utilizar para la transferencia de datos mediante protocolo de enlace bidireccional . Esto significa que los datos se pueden introducir o extraer en las mismas ocho líneas (PA0 - PA7). Los pines PC3 - PC7 se utilizan como líneas de protocolo de enlace para el puerto A. Los pines restantes del puerto C (PC0 - PC2) se pueden utilizar como líneas de entrada/salida si el grupo B se inicializa en el modo 0 o como protocolo de enlace para el puerto B si el grupo B se inicializa en el modo 1. En este modo, el 8255 se puede utilizar para ampliar el bus del sistema a un microprocesador esclavo o para transferir bytes de datos hacia y desde un controlador de disquete . Se proporcionan señales de reconocimiento y protocolo de enlace para mantener el flujo de datos y la sincronización adecuados entre el transmisor y el receptor de datos.