El 8086 [3] (también llamado iAPX 86 ) [4] es un chip microprocesador de 16 bits diseñado por Intel entre principios de 1976 y el 8 de junio de 1978, cuando fue lanzado. El Intel 8088 , lanzado el 1 de julio de 1979, [5] es un chip ligeramente modificado con un bus de datos externo de 8 bits (que permite el uso de circuitos integrados de soporte más baratos y menos numerosos ), [nota 1] y es notable por ser el procesador utilizado en el diseño original de IBM PC .

El 8086 dio origen a la arquitectura x86 , que finalmente se convirtió en la línea de procesadores más exitosa de Intel. El 5 de junio de 2018, Intel lanzó una CPU de edición limitada para celebrar el 40.° aniversario del Intel 8086, llamada Intel Core i7-8086K . [5] [ enlace muerto ]

En 1972, Intel lanzó el 8008 , el primer microprocesador de 8 bits de Intel. [nota 2] Implementaba un conjunto de instrucciones diseñado por Datapoint Corporation con terminales CRT programables en mente, que también resultó ser bastante de propósito general. El dispositivo necesitaba varios circuitos integrados adicionales para producir una computadora funcional, en parte debido a que estaba empaquetado en un pequeño "paquete de memoria" de 18 pines, lo que descartaba el uso de un bus de direcciones separado (Intel era principalmente un fabricante de DRAM en ese momento).

Dos años después, Intel lanzó el 8080 , que empleaba los nuevos paquetes DIL de 40 pines desarrollados originalmente para circuitos integrados de calculadoras para habilitar un bus de direcciones independiente. Tenía un conjunto de instrucciones extendido que es compatible con la fuente (no compatible con binarios ) con el 8008 [6] y también incluía algunas instrucciones de 16 bits para facilitar la programación. El dispositivo 8080 fue finalmente reemplazado por el 8085 (1977) basado en carga de agotamiento , que usaba una única fuente de alimentación de +5 V en lugar de los tres voltajes operativos diferentes de los chips anteriores. [nota 3] Otros microprocesadores de 8 bits bien conocidos que surgieron durante estos años son Motorola 6800 (1974), General Instrument PIC16X (1975), MOS Technology 6502 (1975), Zilog Z80 (1976) y Motorola 6809 (1978).

El proyecto 8086 comenzó en mayo de 1976 y originalmente fue pensado como un sustituto temporal del ambicioso y retrasado proyecto iAPX 432. Fue un intento de desviar la atención de los procesadores de 16 y 32 bits menos retrasados de otros fabricantes: Motorola , Zilog y National Semiconductor .

Mientras que el 8086 era un microprocesador de 16 bits, utilizaba la misma microarquitectura que los microprocesadores de 8 bits de Intel (8008, 8080 y 8085). Esto permitió que los programas en lenguaje ensamblador escritos en 8 bits migraran sin problemas . [7] Se agregaron nuevas instrucciones y características, como números enteros con signo, direccionamiento base+offset y operaciones autorrepetitivas. Se agregaron instrucciones para ayudar a la compilación de código fuente de funciones anidadas en la familia de lenguajes ALGOL , incluidos Pascal y PL/M . Según el arquitecto principal Stephen P. Morse , esto fue el resultado de un enfoque más centrado en el software. Otras mejoras incluyeron instrucciones de microcódigo para las instrucciones de multiplicación y división en lenguaje ensamblador. Los diseñadores también anticiparon coprocesadores , como 8087 y 8089 , por lo que la estructura del bus se diseñó para ser flexible.

La primera revisión del conjunto de instrucciones y la arquitectura de alto nivel estuvo lista después de aproximadamente tres meses, [nota 4] y como casi no se utilizaron herramientas CAD, cuatro ingenieros y 12 personas de diseño trabajaron simultáneamente en el chip. [nota 5] El 8086 tardó un poco más de dos años desde la idea hasta el producto funcional, lo que se consideró rápido para un diseño complejo en la década de 1970.

El 8086 fue secuenciado [nota 6] usando una mezcla de lógica aleatoria [8] y microcódigo y fue implementado usando circuitos nMOS de carga de agotamiento con aproximadamente 20.000 transistores activos (29.000 contando todos los sitios ROM y PLA ). Pronto fue trasladado a un nuevo proceso de fabricación nMOS refinado llamado HMOS (por High performance MOS) que Intel desarrolló originalmente para la fabricación de productos de RAM estática rápida . [nota 7] A esto le siguieron las versiones HMOS-II, HMOS-III y, finalmente, una versión CMOS completamente estática para dispositivos alimentados por batería, fabricada usando los procesos CHMOS de Intel . [nota 8] El chip original medía 33 mm² y el tamaño mínimo de característica era 3,2 μm. Las instrucciones MUL y DIV eran muy lentas debido a que estaban microcodificadas , por lo que los programadores x86 generalmente usaban las instrucciones de desplazamiento de bits para multiplicar y dividir en su lugar. [ cita requerida ]

El chip 8086 se redujo a 2 μm en 1981; esta versión también corrigió un error en el registro de pila de los chips originales de 3,5 μm. Más tarde, las variantes de 1,5 μm y CMOS se subcontrataron a otros fabricantes y no se desarrollaron internamente.

La arquitectura fue definida por Stephen P. Morse con algo de ayuda de Bruce Ravenel (el arquitecto del 8087) en el refinamiento de las revisiones finales. El diseñador lógico Jim McKevitt y John Bayliss fueron los ingenieros principales del equipo de desarrollo a nivel de hardware [nota 9] y Bill Pohlman el gerente del proyecto. El legado del 8086 perdura en el conjunto de instrucciones básicas de los servidores y computadoras personales actuales; el 8086 también prestó sus dos últimos dígitos a versiones extendidas posteriores del diseño, como el Intel 286 y el Intel 386 , todos los cuales eventualmente se conocieron como la familia x86 . (Otra referencia es que el PCI Vendor ID para dispositivos Intel es 8086 h ).

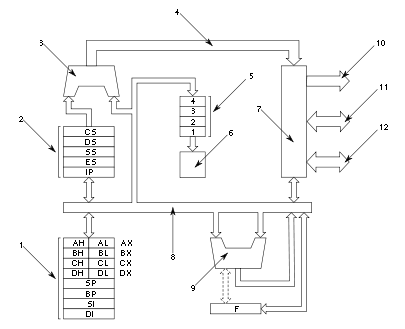

Todos los registros internos, así como los buses de datos internos y externos, tienen 16 bits de ancho, lo que estableció firmemente la identidad de "microprocesador de 16 bits" del 8086. Un bus de dirección externo de 20 bits proporciona un espacio de dirección física de 1 MiB (2 20 = 1.048.576 x 1 byte ). Este espacio de dirección se direcciona mediante la "segmentación" de la memoria interna. El bus de datos se multiplexa con el bus de dirección para que todas las líneas de control quepan en un paquete estándar de doble línea de 40 pines . Proporciona un bus de dirección de E/S de 16 bits, que admite 64 KB de espacio de E/S separado. El espacio de dirección lineal máximo está limitado a 64 KB, simplemente porque los registros de índice/dirección internos tienen solo 16 bits de ancho. La programación sobre límites de memoria de 64 KB implica ajustar los registros de segmento (ver a continuación); Esta dificultad existió hasta que la arquitectura 80386 introdujo registros más anchos (32 bits) (el hardware de administración de memoria en el 80286 no ayudó en este sentido, ya que sus registros todavía tienen solo 16 bits de ancho).

Algunos de los pines de control, que llevan señales esenciales para todas las operaciones externas, tienen más de una función dependiendo de si el dispositivo se opera en modo mínimo o máximo . El primer modo está pensado para sistemas pequeños de un solo procesador, mientras que el segundo es para sistemas medianos o grandes que utilizan más de un procesador (una especie de modo multiprocesador). El modo máximo es necesario cuando se utiliza un coprocesador 8087 o 8089. El voltaje en el pin 33 (MN/ MX ) determina el modo. Cambiar el estado del pin 33 cambia la función de otros pines, la mayoría de los cuales tienen que ver con la forma en que la CPU maneja el bus (local). [nota 10] El modo suele estar cableado en el circuito y, por lo tanto, no se puede cambiar mediante software. El funcionamiento de estos modos se describe en términos de diagramas de tiempo en las hojas de datos y manuales de Intel. En el modo mínimo, todas las señales de control son generadas por el propio 8086.

El 8086 tiene ocho registros más o menos generales de 16 bits (incluido el puntero de pila , pero excluidos el puntero de instrucción, el registro de indicadores y los registros de segmento). Cuatro de ellos, AX, BX, CX, DX, también se pueden acceder como pares de registros de 8 bits (consulte la figura), mientras que los otros cuatro, SI, DI, BP, SP, son solo de 16 bits.

Debido a una codificación compacta inspirada en los procesadores de 8 bits, la mayoría de las instrucciones son operaciones de una o dos direcciones, lo que significa que el resultado se almacena en uno de los operandos. Como máximo, uno de los operandos puede estar en la memoria, pero este operando de memoria también puede ser el destino , mientras que el otro operando, el origen , puede ser registro o inmediato . A menudo, también se puede utilizar una única ubicación de memoria como origen y destino , lo que, entre otros factores, contribuye aún más a una densidad de código comparable a (y a menudo mejor que) la de la mayoría de las máquinas de ocho bits de la época.

El grado de generalidad de la mayoría de los registros es mucho mayor que en el 8080 o el 8085. Sin embargo, los registros del 8086 eran más especializados que en la mayoría de las minicomputadoras contemporáneas y también se usan implícitamente en algunas instrucciones. Si bien es perfectamente sensato para el programador ensamblador, esto hace que la asignación de registros para los compiladores sea más complicada en comparación con los procesadores de 16 y 32 bits más ortogonales de la época, como el PDP-11 , VAX , 68000 , 32016 , etc. Por otro lado, al ser más regulares que los microprocesadores de 8 bits bastante minimalistas pero omnipresentes, como el 6502 , 6800 , 6809 , 8085 , MCS-48 , 8051 y otras máquinas contemporáneas basadas en acumuladores, es significativamente más fácil construir un generador de código eficiente para la arquitectura del 8086.

Otro factor para esto es que el 8086 también introdujo algunas instrucciones nuevas (no presentes en el 8080 y 8085) para soportar mejor los lenguajes de programación de alto nivel basados en pila como Pascal y PL/M ; algunas de las instrucciones más útiles son , y ret size , que soportan la " convención de llamada de Pascal " directamente. (Varias otras, como y , se agregaron en los procesadores 80186, 80286 y 80386 posteriores).push mem-op push immedenter

El hardware admite una pila de 64 KB (un segmento) que crece hacia direcciones inferiores ; las palabras de 16 bits se insertan en la pila y SS:SP apunta a la parte superior de la pila. Hay 256 interrupciones que pueden ser invocadas tanto por hardware como por software. Las interrupciones pueden funcionar en cascada, utilizando la pila para almacenar las direcciones de retorno .

El 8086 tiene 64 K de espacio de puerto de E/S de 8 bits (o alternativamente 32 K de palabra de 16 bits) .

El 8086 tiene un registro de indicadores de 16 bits . Nueve de estos indicadores de código de condición están activos e indican el estado actual del procesador: Indicador de acarreo (CF), Indicador de paridad (PF), Indicador de acarreo auxiliar (AF), Indicador de cero (ZF), Indicador de signo (SF), Indicador de trampa (TF), Indicador de interrupción (IF), Indicador de dirección (DF) e Indicador de desbordamiento (OF). También conocido como palabra de estado, el diseño del registro de indicadores es el siguiente: [9]

También hay cuatro registros de segmento de 16 bits (ver figura) que permiten a la CPU 8086 acceder a un megabyte de memoria de una manera inusual. En lugar de concatenar el registro de segmento con el registro de dirección, como en la mayoría de los procesadores cuyo espacio de dirección excede el tamaño de su registro, el 8086 desplaza el segmento de 16 bits solo cuatro bits antes de agregarlo al desplazamiento de 16 bits (16×segmento + desplazamiento), produciendo así una dirección externa (o efectiva o física) de 20 bits a partir del par segmento:desplazamiento de 32 bits. Como resultado, cada dirección externa puede ser referenciada por 2 12 = 4096 pares segmento:desplazamiento diferentes.

Aunque muchos programadores lo consideran complicado y engorroso, este esquema también tiene ventajas: se puede cargar un programa pequeño (de menos de 64 KB) comenzando en un desplazamiento fijo (como 0000) en su propio segmento, evitando la necesidad de reubicación , con un máximo de 15 bytes de desperdicio de alineación.

Los compiladores de la familia 8086 admiten comúnmente dos tipos de punteros , cercanos y lejanos . Los punteros cercanos son desplazamientos de 16 bits asociados implícitamente con el código del programa o segmento de datos y, por lo tanto, solo se pueden usar dentro de partes de un programa lo suficientemente pequeñas como para caber en un segmento. Los punteros lejanos son pares segmento:desplazamiento de 32 bits que se resuelven en direcciones externas de 20 bits. Algunos compiladores también admiten punteros enormes , que son como punteros lejanos excepto que la aritmética de punteros en un puntero enorme lo trata como un puntero lineal de 20 bits, mientras que la aritmética de punteros en un puntero lejano se envuelve dentro de su desplazamiento de 16 bits sin tocar la parte del segmento de la dirección.

Para evitar la necesidad de especificar proximidad y lejanía en numerosos punteros, estructuras de datos y funciones, los compiladores también admiten "modelos de memoria" que especifican tamaños de puntero predeterminados. Los modelos diminuto (máximo 64 K), pequeño (máximo 128 K), compacto (datos > 64 K), mediano (código > 64 K), grande (código, datos > 64 K) y enorme (matrices individuales > 64 K) cubren combinaciones prácticas de punteros cercanos, lejanos y enormes para código y datos. El modelo diminuto significa que el código y los datos se comparten en un solo segmento, al igual que en la mayoría de los procesadores basados en 8 bits, y se puede utilizar para crear archivos .com, por ejemplo. Las bibliotecas precompiladas a menudo vienen en varias versiones compiladas para diferentes modelos de memoria.

Según Morse et al., [10] los diseñadores en realidad contemplaron utilizar un desplazamiento de 8 bits (en lugar de 4 bits) para crear un espacio de dirección física de 16 MB. Sin embargo, como esto habría obligado a que los segmentos comenzaran en límites de 256 bytes, y 1 MB se consideraba demasiado grande para un microprocesador alrededor de 1976, la idea fue descartada. Además, no había suficientes pines disponibles en un paquete de 40 pines de bajo costo para los cuatro pines adicionales del bus de direcciones.

En principio, el espacio de direcciones de la serie x86 podría haberse ampliado en procesadores posteriores incrementando el valor de desplazamiento, siempre y cuando las aplicaciones obtuvieran sus segmentos del sistema operativo y no hicieran suposiciones sobre la equivalencia de diferentes pares segmento:desplazamiento. [nota 11] En la práctica, el uso de punteros "enormes" y mecanismos similares estaba muy extendido y el direccionamiento plano de 32 bits que se hizo posible con los registros de desplazamiento de 32 bits en el 80386 eventualmente extendió el rango de direccionamiento limitado de una manera más general.

El flujo de instrucciones se recupera de la memoria en forma de palabras y el procesador lo direcciona internamente al nivel de bytes según sea necesario. Un mecanismo de cola de flujo de instrucciones permite poner en cola hasta 6 bytes del flujo de instrucciones mientras se espera la decodificación y la ejecución. La cola actúa como un búfer FIFO (First-In-First-Out), del que la unidad de ejecución (UE) extrae bytes de instrucciones según sea necesario. Siempre que haya espacio para al menos dos bytes en la cola, la BIU intentará un ciclo de memoria de búsqueda de palabras. Si la cola está vacía (después de una instrucción de bifurcación, por ejemplo), el primer byte en la cola queda inmediatamente disponible para la UE. [11]

Los programas pequeños podían ignorar la segmentación y utilizar simplemente un direccionamiento de 16 bits. Esto permite que el software de 8 bits se pueda trasladar con bastante facilidad al 8086. Los autores de la mayoría de las implementaciones de DOS aprovecharon esta ventaja proporcionando una interfaz de programación de aplicaciones muy similar a CP/M, además de incluir el sencillo formato de archivo ejecutable .com , idéntico al de CP/M. Esto era importante cuando el 8086 y MS-DOS eran nuevos, porque permitía que muchas aplicaciones CP/M (y otras) existentes estuvieran disponibles rápidamente, lo que facilitó enormemente la aceptación de la nueva plataforma.

El siguiente código fuente de ensamblaje 8086 corresponde a una subrutina llamada que copia una cadena de caracteres ASCIIZ_strtolower terminada en cero de una ubicación a otra, convirtiendo todos los caracteres alfabéticos a minúsculas. La cadena se copia un byte (carácter de 8 bits) a la vez.

El código de ejemplo utiliza el registro BP (puntero base) para establecer un marco de llamada , un área en la pila que contiene todos los parámetros y variables locales para la ejecución de la subrutina. Este tipo de convención de llamada admite código reentrante y recursivo y ha sido utilizada por lenguajes similares a Algol desde fines de la década de 1950. Se supone un modelo de memoria plana, específicamente, que los segmentos DS y ES abordan la misma región de memoria.

Aunque en parte se ven eclipsados por otras opciones de diseño en este chip en particular, los buses de datos y direcciones multiplexados limitan ligeramente el rendimiento; las transferencias de cantidades de 16 bits u 8 bits se realizan en un ciclo de acceso a memoria de cuatro relojes, que es más rápido en 16 bits, aunque más lento en cantidades de 8 bits, en comparación con muchas CPU contemporáneas basadas en 8 bits. Como las instrucciones varían de uno a seis bytes, la búsqueda y la ejecución se realizan simultáneamente y se desacoplan en unidades separadas (como sigue siendo en los procesadores x86 actuales): la unidad de interfaz de bus alimenta el flujo de instrucciones a la unidad de ejecución a través de una cola de prebúsqueda de 6 bytes (una forma de canalización de acoplamiento flexible ), acelerando las operaciones en registros e inmediatos , mientras que las operaciones de memoria se volvieron más lentas (cuatro años después, este problema de rendimiento se solucionó con el 80186 y el 80286 ). Sin embargo, la arquitectura completa (en lugar de parcial) de 16 bits con una ALU de ancho completo significó que las instrucciones aritméticas de 16 bits ahora se podían realizar con un solo ciclo de ALU (en lugar de dos, a través de acarreo interno, como en el 8080 y 8085), acelerando considerablemente dichas instrucciones. Combinado con ortogonalizaciones de operaciones versus tipos de operandos y modos de direccionamiento , así como otras mejoras, esto hizo que la ganancia de rendimiento sobre el 8080 o 8085 fuera bastante significativa, a pesar de los casos en los que los chips más antiguos pueden ser más rápidos (ver a continuación).

Como se puede ver en estas tablas, las operaciones sobre registros e inmediatos eran rápidas (entre 2 y 4 ciclos), mientras que las instrucciones sobre operandos de memoria y los saltos eran bastante lentos; los saltos llevaban más ciclos que en los sencillos 8080 y 8085 , y el 8088 (utilizado en el IBM PC) se veía además obstaculizado por su bus más estrecho. Las razones por las que la mayoría de las instrucciones relacionadas con la memoria eran lentas eran tres:

Sin embargo, el rendimiento del acceso a la memoria mejoró drásticamente con la siguiente generación de CPU de la familia 8086 de Intel. Tanto el 80186 como el 80286 tenían hardware de cálculo de direcciones dedicado, lo que ahorraba muchos ciclos, y el 80286 también tenía buses de datos y direcciones separados (no multiplexados).

El 8086/8088 se podía conectar a un coprocesador matemático para añadir rendimiento de punto flotante basado en hardware/microcódigo . El Intel 8087 era el coprocesador matemático estándar para el 8086 y el 8088, y funcionaba con números de 80 bits. Fabricantes como Cyrix (compatible con el 8087) y Weitek ( no compatible con el 8087) acabaron creando coprocesadores de punto flotante de alto rendimiento que competían con el 8087.

La frecuencia de reloj estaba originalmente limitada a 5 MHz, [nota 12] pero las últimas versiones en HMOS fueron especificadas para 10 MHz. Las versiones HMOS-III y CMOS se fabricaron durante mucho tiempo (al menos hasta bien entrada la década de 1990) para sistemas integrados, aunque su sucesor, el 80186/80188 ( que incluye algunos periféricos en chip), ha sido más popular para uso integrado.

El 80C86, la versión CMOS del 8086, se utilizó en el GRiDPad , Toshiba T1200 , HP 110 y, finalmente, en el Lunar Prospector de 1998-1999 .

Para el embalaje, el Intel 8086 estaba disponible en paquetes DIP de cerámica y plástico.

Fujitsu , [23] Harris / Intersil , OKI , Siemens , Texas Instruments , NEC , Mitsubishi y AMD fabricaron versiones compatibles (y, en muchos casos, mejoradas) . Por ejemplo, el par NEC V20 y NEC V30 eran compatibles en hardware con el 8088 y el 8086, aunque NEC fabricó clones originales de Intel, μPD8088D y μPD8086D, respectivamente, pero incorporaban el conjunto de instrucciones del 80186 junto con algunas (pero no todas) de las mejoras de velocidad del 80186, lo que proporcionaba una capacidad inmediata para actualizar tanto el conjunto de instrucciones como la velocidad de procesamiento sin que los fabricantes tuvieran que modificar sus diseños. Estos procesadores relativamente simples y de bajo consumo compatibles con el 8086 en CMOS todavía se utilizan en sistemas integrados.

La industria electrónica de la Unión Soviética fue capaz de replicar el 8086 mediante espionaje industrial e ingeniería inversa [ cita requerida ] . El chip resultante, K1810VM86 , era compatible a nivel binario y de pines con el 8086.

i8086 e i8088 fueron respectivamente los núcleos de los ordenadores de sobremesa EC1831 y EC1832 compatibles con PC de fabricación soviética. (EC1831 es la identificación EC de IZOT 1036C y EC1832 es la identificación EC de IZOT 1037C, desarrollados y fabricados en Bulgaria. EC significa Единая Система.) Sin embargo, el ordenador EC1831 (IZOT 1036C) tenía diferencias de hardware significativas con respecto al prototipo de IBM PC. El EC1831 fue el primer ordenador compatible con PC con dimensionamiento de bus dinámico (Patente de EE. UU. N.º 4.831.514). Posteriormente, algunos de los principios EC1831 se adoptaron en PS/2 (Patente de EE. UU. N.° 5.548.786) y algunas otras máquinas (Solicitud de Patente del Reino Unido, Publicación N.° GB-A-2211325, publicada el 28 de junio de 1989).

[…] El 8086 es compatible con el 8080 a nivel de lenguaje ensamblador. […]

Los tiempos y codificaciones de este manual se utilizan con permiso de Intel y proceden de las siguientes publicaciones: Intel Corporation. Manual del usuario de iAPX 86, 88, 186 y 188, Referencia del programador, Santa Clara, California, 1986.(De manera similar para iAPX 286, 80386, 80387).

los IBM PC (1981) y PC/XT (1983) originales, el FDC se encontraba físicamente en una tarjeta adaptadora de disquete independiente. El propio FDC era un NEC μPD765A o una pieza compatible, como el Intel 8272A.

El IBM Displaywriter es notablemente más caro que otros microprocesadores industriales que utilizan el 8086.