Un ADC integrador es un tipo de convertidor analógico a digital que convierte un voltaje de entrada desconocido en una representación digital mediante el uso de un integrador . En su implementación básica, el convertidor de doble pendiente, el voltaje de entrada desconocido se aplica a la entrada del integrador y se le permite aumentar gradualmente durante un período de tiempo fijo (el período de aceleración). Luego, se aplica un voltaje de referencia conocido de polaridad opuesta al integrador y se le permite aumentar gradualmente hasta que la salida del integrador vuelva a cero (el período de desaceleración). El voltaje de entrada se calcula como una función del voltaje de referencia, el período de aceleración constante y el período de desaceleración medido. La medición del tiempo de desaceleración generalmente se realiza en unidades del reloj del convertidor, por lo que los tiempos de integración más largos permiten resoluciones más altas. Asimismo, la velocidad del convertidor se puede mejorar sacrificando la resolución.

Los convertidores de este tipo pueden lograr una alta resolución, pero a menudo lo hacen a expensas de la velocidad. Por este motivo, estos convertidores no se encuentran en aplicaciones de procesamiento de audio o señales. Su uso se limita normalmente a voltímetros digitales y otros instrumentos que requieren mediciones de gran precisión.

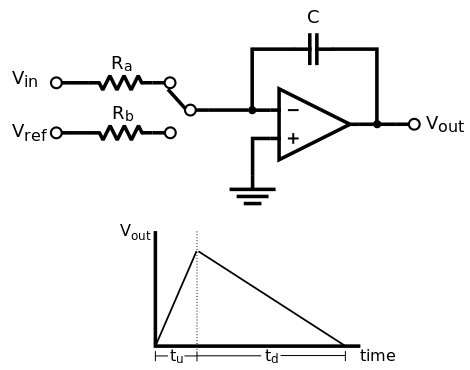

El circuito ADC integrador básico consta de un integrador, un interruptor para seleccionar entre el voltaje que se va a medir y el voltaje de referencia, un temporizador que determina cuánto tiempo se tarda en integrar lo desconocido y mide cuánto tiempo tardó la integración de referencia, un comparador para detectar el cruce por cero y un controlador. Según la implementación, también puede haber un interruptor en paralelo con el condensador integrador para permitir que el integrador se reinicie. Las entradas del controlador incluyen un reloj (que se utiliza para medir el tiempo) y la salida de un comparador que se utiliza para detectar cuándo la salida del integrador llega a cero.

La conversión se lleva a cabo en dos fases: la fase de arranque, donde la entrada al integrador es el voltaje que se va a medir, y la fase de desaceleración, donde la entrada al integrador es un voltaje de referencia conocido. Durante la fase de arranque, el interruptor selecciona el voltaje medido como entrada al integrador. Se permite que el integrador se active durante un período de tiempo fijo para permitir que se acumule una carga en el condensador del integrador. Durante la fase de desaceleración, el interruptor selecciona el voltaje de referencia como entrada al integrador. Durante esta fase se mide el tiempo que tarda la salida del integrador en volver a cero.

Para que el voltaje de referencia haga descender el voltaje del integrador, el voltaje de referencia debe tener una polaridad opuesta a la del voltaje de entrada. En la mayoría de los casos, para voltajes de entrada positivos, esto significa que el voltaje de referencia será negativo. Para manejar voltajes de entrada positivos y negativos, se requiere un voltaje de referencia positivo y negativo. La selección de qué referencia utilizar durante la fase de desaceleración se basaría en la polaridad de la salida del integrador al final de la fase de aceleración.

La ecuación básica para la salida del integrador (asumiendo una entrada constante) es:

Suponiendo que el voltaje del integrador inicial al inicio de cada conversión es cero y que el voltaje del integrador al final del período de desaceleración será cero, tenemos las siguientes dos ecuaciones que cubren la salida del integrador durante las dos fases de la conversión:

Las dos ecuaciones se pueden combinar y resolver para el voltaje de entrada desconocido:

De la ecuación se desprende una de las ventajas del ADC integrador de doble pendiente: la medición es independiente de los valores de los elementos del circuito (R y C). Sin embargo, esto no significa que los valores de R y C no sean importantes en el diseño de un ADC integrador de doble pendiente (como se explicará más adelante).

Tenga en cuenta que en el gráfico, el voltaje se muestra como ascendente durante la fase de aceleración y descendente durante la fase de desaceleración. En realidad, debido a que el integrador utiliza el amplificador operacional en una configuración de retroalimentación negativa, aplicar una positiva hará que la salida del integrador disminuya . El aumento y la disminución se refieren con mayor precisión al proceso de agregar carga al capacitor del integrador durante la fase de aceleración y eliminar carga durante la fase de desaceleración.

La resolución del ADC integrador de doble pendiente está determinada principalmente por la duración del período de desaceleración y por la resolución de la medición del tiempo (es decir, la frecuencia del reloj del controlador). La resolución requerida (en número de bits) dicta la duración mínima del período de desaceleración para una entrada de escala completa (por ejemplo ):

Durante la medición de una entrada de escala completa, la pendiente de la salida del integrador será la misma durante las fases de aceleración y desaceleración. Esto también implica que el tiempo del período de aceleración y el período de desaceleración serán iguales ( ) y que el tiempo total de medición será . Por lo tanto, el tiempo total de medición para una entrada de escala completa se basará en la resolución deseada y la frecuencia del reloj del controlador:

Normalmente, el tiempo de arranque se elige para que sea un múltiplo del período de la frecuencia de la red , para suprimir el zumbido de la red.

Existen límites para la resolución máxima del ADC integrador de doble pendiente. No es posible aumentar la resolución del ADC de doble pendiente básico a valores arbitrariamente altos mediante el uso de tiempos de medición más prolongados o relojes más rápidos. La resolución está limitada por:

El diseño básico del convertidor analógico-digital de doble pendiente tiene limitaciones en cuanto a linealidad, velocidad de conversión y resolución. Se han realizado varias modificaciones al diseño básico para superarlas en cierta medida.

La fase de aceleración del diseño básico de doble pendiente integra el voltaje de entrada durante un período de tiempo fijo. Es decir, permite que se acumule una cantidad desconocida de carga en el capacitor del integrador. La fase de desaceleración se utiliza luego para medir esta carga desconocida y determinar el voltaje desconocido. Para una entrada de escala completa igual al voltaje de referencia, la mitad del tiempo de medición se dedica a la fase de aceleración. Reducir la cantidad de tiempo empleado en la fase de aceleración puede reducir el tiempo total de medición. Una implementación común utiliza un rango de entrada dos veces más grande que el voltaje de referencia.

Una forma sencilla de reducir el tiempo de arranque es aumentar la velocidad a la que se acumula la carga en el condensador integrador reduciendo el tamaño de la resistencia utilizada en la entrada. Esto permite la misma cantidad total de acumulación de carga, pero lo hace durante un período de tiempo más corto. El uso del mismo algoritmo para la fase de deceleración da como resultado la siguiente ecuación para el cálculo del voltaje de entrada desconocido ( ):

Tenga en cuenta que esta ecuación, a diferencia de la ecuación del convertidor de doble pendiente básico, depende de los valores de las resistencias del integrador. O, lo que es más importante, depende de la relación entre los dos valores de resistencia. Esta modificación no mejora en nada la resolución del convertidor (ya que no aborda ninguna de las limitaciones de resolución mencionadas anteriormente).

El propósito de la fase de aceleración es agregar una carga proporcional al voltaje de entrada al integrador para que se mida posteriormente durante la fase de desaceleración. Un método para mejorar la resolución del convertidor es aumentar artificialmente el rango del amplificador integrador durante la fase de aceleración. Un método para aumentar la capacidad del integrador es agregar o restar periódicamente cantidades conocidas de carga durante la fase de aceleración para mantener la salida del integrador dentro del rango del amplificador integrador. La carga total acumulada es la carga introducida por el voltaje de entrada desconocido más la suma de las cargas conocidas que se agregaron o restaron.

El diagrama de circuito que se muestra a la derecha es un ejemplo de cómo se podría implementar el arranque con múltiples pendientes. Durante el arranque, el voltaje de entrada desconocido, , siempre se aplica al integrador. Los voltajes de referencia positivos y negativos controlados por los dos interruptores independientes suman y restan carga según sea necesario para mantener la salida del integrador dentro de sus límites. Las resistencias de referencia, y son necesariamente más pequeñas que para garantizar que las referencias puedan superar la carga introducida por la entrada. Se utiliza un comparador conectado a la salida del integrador para decidir qué voltaje de referencia se debe aplicar. Este puede ser un algoritmo relativamente simple: si la salida del integrador está por encima del umbral, habilite la referencia positiva (para hacer que la salida baje); si la salida del integrador está por debajo del umbral, habilite la referencia negativa (para hacer que la salida suba). El controlador realiza un seguimiento de la frecuencia con la que se enciende cada interruptor para tener en cuenta la carga adicional colocada (o eliminada) del condensador del integrador como resultado de los voltajes de referencia. La carga agregada/resta durante el proceso de subida de múltiples pendientes forma la parte gruesa del resultado (por ejemplo, los 3 dígitos iniciales).

A la derecha se muestra un gráfico de la salida de muestra del integrador durante un período de aceleración de múltiples pendientes. Cada línea vertical discontinua representa un punto de decisión del controlador en el que toma una muestra de la polaridad de la salida y elige aplicar el voltaje de referencia positivo o negativo a la entrada. Idealmente, el voltaje de salida del integrador al final del período de aceleración se puede representar mediante la siguiente ecuación:

donde es el período de muestreo, es el número de períodos en los que se activa la referencia positiva, es el número de períodos en los que se activa la referencia negativa y es el número total de períodos en la fase de preparación.

La resolución obtenida durante el run-up viene dada por el número de períodos del algoritmo run-up. El run-up multi-pendiente tiene múltiples ventajas:

Si bien es posible continuar con el proceso de aceleración de múltiples pendientes de manera indefinida, no es posible aumentar la resolución del convertidor a niveles arbitrariamente altos simplemente utilizando un tiempo de aceleración más largo. Se introducen errores en el proceso de aceleración de múltiples pendientes a través de la acción de los interruptores que controlan las referencias, el acoplamiento cruzado entre los interruptores, la inyección de carga no intencionada de los interruptores, los desajustes en las referencias y los errores de sincronización. [3]

Parte de este error se puede reducir mediante el funcionamiento cuidadoso de los interruptores. [4] [5] En particular, durante el período de arranque, cada interruptor debe activarse una cantidad constante de veces. El algoritmo explicado anteriormente no hace esto y solo alterna los interruptores según sea necesario para mantener la salida del integrador dentro de los límites. Activar cada interruptor una cantidad constante de veces hace que el error relacionado con la conmutación sea aproximadamente constante. Cualquier desviación de salida que sea resultado del error de conmutación se puede medir y luego restar numéricamente del resultado.

El método de reducción de pendiente simple y de una sola pendiente es lento. Normalmente, el tiempo de reducción de pendiente se mide en ticks de reloj, por lo que para obtener una resolución de cuatro dígitos, el tiempo de reducción de pendiente puede tardar hasta 10.000 ciclos de reloj. Un método de reducción de pendiente múltiple puede acelerar la medición sin sacrificar la precisión. Al utilizar 4 velocidades de pendiente que son cada una una potencia de diez más graduales que la anterior, se puede lograr una resolución de cuatro dígitos en aproximadamente 40 ticks de reloj, una enorme mejora de la velocidad. [6]

El circuito que se muestra a la derecha es un ejemplo de un circuito de reducción de pendiente múltiple con cuatro pendientes de reducción, cada una de las cuales es diez veces más gradual que la anterior. Los interruptores controlan qué pendiente se selecciona. El interruptor que contiene selecciona la pendiente más pronunciada (es decir, hará que la salida del integrador se mueva hacia cero más rápido). Al comienzo del intervalo de reducción, la entrada desconocida se elimina del circuito abriendo el interruptor conectado a y cerrando el interruptor. Una vez que la salida del integrador llega a cero (y se mide el tiempo de reducción), se abre el interruptor y se selecciona la siguiente pendiente cerrando el interruptor. Esto se repite hasta que la pendiente final haya llegado a cero. La combinación de los tiempos de reducción para cada una de las pendientes determina el valor de la entrada desconocida. En esencia, cada pendiente agrega un dígito de resolución al resultado.

El método de reducción de pendiente múltiple se utiliza a menudo en combinación con un método de aumento de pendiente múltiple. El método de aumento de pendiente múltiple permite utilizar un condensador relativamente pequeño en el integrador y, por lo tanto, una pendiente relativamente pronunciada con la que empezar y, por lo tanto, la opción de utilizar pendientes mucho más graduales. Es posible utilizar un método de reducción de pendiente múltiple también con un método de aumento simple (como en el ADC de pendiente doble), pero está limitado por la pendiente relativamente pequeña de la fase inicial y no hay mucho margen para pendientes mucho más pequeñas.

En el circuito de ejemplo, las resistencias de pendiente difieren en un factor de 10. Este valor, conocido como base ( ), puede ser cualquier valor. Como se explica a continuación, la elección de la base afecta la velocidad del convertidor y determina la cantidad de pendientes necesarias para lograr la resolución deseada.

La base de este diseño es la suposición de que siempre habrá un sobreimpulso al intentar encontrar el cruce por cero al final de un intervalo de desaceleración. Esto será así debido al muestreo periódico del comparador basado en el reloj del convertidor. Si suponemos que el convertidor cambia de una pendiente a la siguiente en un solo ciclo de reloj (lo que puede ser posible o no), la cantidad máxima de sobreimpulso para una pendiente dada sería el mayor cambio de salida del integrador en un período de reloj:

Para superar este sobreimpulso, la siguiente pendiente no requeriría más que ciclos de reloj, lo que ayuda a poner un límite al tiempo total de la fase de desaceleración. El tiempo para la primera fase de desaceleración (usando la pendiente más pronunciada) depende de la entrada desconocida (es decir, la cantidad de carga colocada en el capacitor integrador durante la fase de aceleración). Como máximo, será:

donde es el número máximo de períodos de reloj para la primera pendiente, es el voltaje máximo del integrador al inicio de la fase de desaceleración y es la resistencia utilizada para la primera pendiente.

El resto de pendientes tienen una duración limitada en función de la base seleccionada, por lo que el tiempo restante de la conversión (en periodos de reloj del conversor) es:

¿Dónde está el número de pendientes?

La conversión de los intervalos de tiempo medidos durante la reducción de pendiente múltiple en un voltaje medido es similar al método de equilibrio de carga utilizado en la mejora de la reducción de pendiente múltiple. Cada pendiente suma o resta cantidades conocidas de carga al condensador integrador. La reducción habrá agregado una cantidad desconocida de carga al integrador. Luego, durante la reducción, la primera pendiente resta una gran cantidad de carga, la segunda pendiente agrega una cantidad menor de carga, etc., y cada pendiente posterior se mueve una cantidad menor en la dirección opuesta de la pendiente anterior con el objetivo de acercarse cada vez más a cero. Cada pendiente suma o resta una cantidad de carga proporcional a la resistencia de la pendiente y la duración de la pendiente:

es necesariamente un número entero y, idealmente, será menor o igual que para la segunda pendiente y las subsiguientes. Usando el circuito anterior como ejemplo, la segunda pendiente, , puede aportar la siguiente carga, , al integrador:

Es decir, valores posibles con el mayor igual al paso más pequeño de la primera pendiente, o un dígito (base 10) de resolución por pendiente. Generalizando esto, podemos representar el número de pendientes, , en términos de la base y la resolución requerida, :

Sustituyendo esto nuevamente en la ecuación que representa el tiempo de desaceleración requerido para la segunda pendiente y las subsiguientes, obtenemos lo siguiente:

Lo cual, al evaluarlo, muestra que el tiempo mínimo de parada se puede lograr utilizando una base de e . Esta base puede ser difícil de utilizar tanto en términos de complejidad en el cálculo del resultado como de encontrar una red de resistencias adecuada, por lo que una base de 2 o 4 sería más común.

Al utilizar mejoras de aceleración como la aceleración de múltiples pendientes, donde una parte de la resolución del convertidor se resuelve durante la fase de aceleración, es posible eliminar la fase de desaceleración por completo utilizando un segundo tipo de convertidor analógico a digital. [7] Al final de la fase de aceleración de una conversión de aceleración de múltiples pendientes, todavía habrá una cantidad desconocida de carga restante en el condensador del integrador. En lugar de utilizar una fase de desaceleración tradicional para determinar esta carga desconocida, el voltaje desconocido se puede convertir directamente mediante un segundo convertidor y combinarse con el resultado de la fase de aceleración para determinar el voltaje de entrada desconocido.

Suponiendo que se utiliza el arranque de múltiples pendientes como se describe arriba, el voltaje de entrada desconocido se puede relacionar con los contadores de arranque de múltiples pendientes, y , y el voltaje de salida del integrador medido, utilizando la siguiente ecuación (derivada de la ecuación de salida de arranque de múltiples pendientes):

Esta ecuación representa el cálculo teórico del voltaje de entrada suponiendo componentes ideales. Dado que la ecuación depende de casi todos los parámetros del circuito, cualquier variación en las corrientes de referencia, el capacitor integrador u otros valores introducirá errores en el resultado. Normalmente se incluye un factor de calibración en el término para tener en cuenta los errores medidos (o, como se describe en la patente a la que se hace referencia, para convertir la salida del ADC residual en las unidades de los contadores de arranque).

En lugar de utilizarse para eliminar por completo la fase de desaceleración, el ADC residual también se puede utilizar para hacer que la fase de desaceleración sea más precisa de lo que sería posible de otro modo. [8] Con una fase de desaceleración tradicional, el período de medición del tiempo de desaceleración termina con el cruce de cero voltios de la salida del integrador. Existe una cierta cantidad de error involucrado en la detección del cruce por cero utilizando un comparador (una de las deficiencias del diseño básico de doble pendiente como se explicó anteriormente). Al utilizar el ADC residual para muestrear rápidamente la salida del integrador (sincronizado con el reloj del controlador del convertidor, por ejemplo), se puede tomar una lectura de voltaje tanto inmediatamente antes como inmediatamente después del cruce por cero (medido con un comparador). Como la pendiente del voltaje del integrador es constante durante la fase de desaceleración, las dos mediciones de voltaje se pueden utilizar como entradas para una función de interpolación que determina con mayor precisión el momento del cruce por cero (es decir, con una resolución mucho mayor de la que permitiría el reloj del controlador solo).

Al combinar algunas de estas mejoras con el diseño básico de doble pendiente (a saber, el aumento de pendiente múltiple y el ADC residual), es posible construir un convertidor analógico a digital integrador que sea capaz de operar de manera continua sin la necesidad de un intervalo de desaceleración. [9] Conceptualmente, se permite que el algoritmo de aumento de pendiente múltiple funcione de manera continua. Para iniciar una conversión, ocurren dos cosas simultáneamente: se utiliza el ADC residual para medir la carga aproximada que se encuentra actualmente en el capacitor integrador y se reinician los contadores que monitorean el aumento de pendiente múltiple. Al final de un período de conversión, se toma otra lectura del ADC residual y se anotan los valores de los contadores de aumento de pendiente múltiple.

La entrada desconocida se calcula utilizando una ecuación similar a la utilizada para el ADC residual, excepto que se incluyen dos voltajes de salida ( que representan el voltaje del integrador medido al inicio de la conversión y que representan el voltaje del integrador medido al final de la conversión).

Un convertidor de integración continua de este tipo es muy similar a un convertidor analógico a digital delta-sigma .

En la mayoría de las variantes del convertidor integrador de doble pendiente, el rendimiento del convertidor depende de uno o más parámetros del circuito. En el caso del diseño básico, la salida del convertidor se expresa en términos de la tensión de referencia. En diseños más avanzados, también existen dependencias de una o más resistencias utilizadas en el circuito o del condensador integrador que se esté utilizando. En todos los casos, incluso si se utilizan componentes de precisión costosos, puede haber otros efectos que no se tienen en cuenta en las ecuaciones generales de doble pendiente (efecto dieléctrico en el condensador o dependencias de frecuencia o temperatura en cualquiera de los componentes). Cualquiera de estas variaciones da como resultado un error en la salida del convertidor. En el mejor de los casos, se trata simplemente de un error de ganancia o de compensación. En el peor de los casos, podría producirse no linealidad o no monotonía.

Algunas calibraciones se pueden realizar internamente en el convertidor (es decir, sin necesidad de ninguna entrada externa especial). Este tipo de calibración se realizaría cada vez que se encienda el convertidor, periódicamente mientras el convertidor esté en funcionamiento o solo cuando se ingrese a un modo de calibración especial. Otro tipo de calibración requiere entradas externas de cantidades conocidas (por ejemplo, estándares de voltaje o referencias de resistencia de precisión) y, por lo general, se realizaría con poca frecuencia (cada año para equipos utilizados en condiciones normales, con mayor frecuencia cuando se utilizan en aplicaciones de metrología ).

De estos tipos de error, el error de compensación es el más sencillo de corregir (suponiendo que existe una compensación constante en todo el rango del convertidor). Esto se suele hacer internamente en el propio convertidor tomando medidas periódicas del potencial de tierra. Lo ideal es que la medición de la tierra siempre dé como resultado una salida de cero. Cualquier salida distinta de cero indica el error de compensación en el convertidor. Es decir, si la medición de la tierra dio como resultado una salida de 0,001 voltios, se puede suponer que todas las mediciones tendrán una compensación de la misma cantidad y se puede restar 0,001 de todos los resultados posteriores.

El error de ganancia se puede medir y corregir de manera similar internamente (nuevamente suponiendo que existe un error de ganancia constante en todo el rango de salida). La referencia de voltaje (o algún voltaje derivado directamente de la referencia) se puede utilizar como entrada al convertidor. Si se asume que la referencia de voltaje es precisa (dentro de las tolerancias del convertidor) o que la referencia de voltaje se ha calibrado externamente con respecto a un estándar de voltaje, cualquier error en la medición sería un error de ganancia en el convertidor. Si, por ejemplo, la medición de la referencia de 5 voltios de un convertidor dio como resultado una salida de 5,3 voltios (después de tener en cuenta cualquier error de compensación), se puede aplicar un multiplicador de ganancia de 0,94 (5 / 5,3) a cualquier resultado de medición posterior.