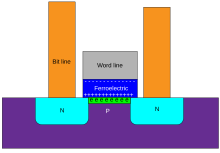

Un transistor de efecto de campo ferroeléctrico ( Fe FET ) es un tipo de transistor de efecto de campo que incluye un material ferroeléctrico intercalado entre el electrodo de puerta y la región de conducción fuente-drenaje del dispositivo (el canal ). La polarización permanente del campo eléctrico en el ferroeléctrico hace que este tipo de dispositivo conserve el estado del transistor (encendido o apagado) en ausencia de cualquier polarización eléctrica.

Los dispositivos basados en FeFET se utilizan en la memoria FeFET , un tipo de memoria no volátil de un solo transistor .

En 1955, Ian Munro Ross presentó una patente para FeFET o MFSFET. Su estructura era como la de un MOSFET de canal de inversión moderno, pero se utilizó material ferroeléctrico como dieléctrico/aislante en lugar de óxido. [1] Moll y Tarui propusieron el uso de un ferroeléctrico ( sulfato de triglicina ) en una memoria de estado sólido en 1963 utilizando un transistor de película delgada . [2] Se realizaron más investigaciones en la década de 1960, pero las características de retención de los dispositivos basados en películas delgadas no fueron satisfactorias. [3] Los primeros dispositivos basados en transistores de efecto de campo utilizaban titanato de bismuto (Bi 4 Ti 3 O 12 ) ferroeléctrico o Pb 1−x Ln x TiO 3 (PLT) y circonatos/titanatos mixtos relacionados ( PLZT ). [3] A finales de 1980 se desarrolló la RAM ferroeléctrica , utilizando una película delgada ferroeléctrica como condensador, conectada a un FET de direccionamiento. [3]

Los dispositivos de memoria basados en FeFET se leen utilizando voltajes por debajo del voltaje coercitivo para el ferroeléctrico. [4]

Los problemas involucrados en la realización de un dispositivo de memoria FeFET práctico incluyen (a partir de 2006): elección de una capa altamente aislante y de alta permitividad entre el ferroeléctrico y la puerta; problemas con la alta polarización remanente de los ferroeléctricos; tiempo de retención limitado (aprox. unos pocos días, cf. se requieren 10 años). [5]

Siempre que la capa ferroeléctrica se pueda escalar en consecuencia, se espera que los dispositivos de memoria basados en FeFET se escalen (encojan) tan bien como los dispositivos MOSFET; sin embargo, puede existir un límite de ~20 nm lateralmente [6] (el límite superparaeléctrico, también conocido como límite ferroeléctrico). Otros desafíos para presentar encogimientos incluyen: espesor reducido de la película que causa efectos de polarización adicionales (no deseados); inyección de carga; y corrientes de fuga. [5]

En 2017, se informó que la memoria no volátil basada en FeFET se había construido en un nodo de 22 nm utilizando FDSOI CMOS ( silicio sobre aislante completamente agotado ) con dióxido de hafnio (HfO 2 ) como ferroeléctrico; el tamaño de celda FeFET más pequeño informado fue de 0,025 μm 2 , el Los dispositivos se construyeron como matrices de 32 Mbit, utilizando pulsos de configuración/reinicio de ~10 ns de duración a 4,2 V; los dispositivos mostraron una resistencia de 10 5 ciclos y una retención de datos de hasta 300 °C. [7]

A partir de 2017, [update]la startup Ferroelectric Memory Company está intentando desarrollar la memoria FeFET en un dispositivo comercial, basado en dióxido de hafnio. Se afirma que la tecnología de la compañía se adapta a los tamaños de los nodos de proceso modernos y se integra con los procesos de producción contemporáneos, es decir, HKMG , y es fácilmente integrable en procesos CMOS convencionales, requiriendo sólo dos máscaras adicionales. [8]