Emotion Engine es una unidad central de procesamiento desarrollada y fabricada por Sony Computer Entertainment y Toshiba para su uso en la consola de videojuegos PlayStation 2 . También se utilizó en los primeros modelos de PlayStation 3 vendidos en Japón y América del Norte (números de modelo CECHAxx y CECHBxx) para brindar soporte para juegos de PlayStation 2. La producción en masa de Emotion Engine comenzó en 1999 y finalizó a finales de 2012 con la descontinuación de PlayStation 2. [1]

El Emotion Engine consta de ocho "unidades" separadas, cada una de las cuales realiza una tarea específica, integradas en el mismo troquel . Estas unidades son: un núcleo de CPU, dos Unidades de Procesamiento Vectorial (VPU), una unidad DMA de 10 canales , un controlador de memoria y una Unidad de Procesamiento de Imágenes (IPU). Hay tres interfaces: una interfaz de entrada y salida para el procesador de E/S, una interfaz de gráficos (GIF) para el sintetizador de gráficos y una interfaz de memoria para la memoria del sistema. [2]

El núcleo de la CPU está estrechamente acoplado a la primera VPU, la VPU 0 . Juntos, son responsables de ejecutar el código del juego y los cálculos de modelado de alto nivel. La segunda VPU, VPU 1 , está dedicada a las transformaciones geométricas y la iluminación y funciona de forma independiente, paralela al núcleo de la CPU, controlada por microcódigo . VPU 0 , cuando no se utiliza, también se puede utilizar para transformaciones de geometría. Las listas de visualización generadas por CPU/VPU0 y VPU1 se envían al GIF, que las prioriza antes de enviarlas al sintetizador de gráficos para su renderización.

El núcleo de la CPU es un procesador RISC en orden superescalar bidireccional . [3] Basado en MIPS R5900, implementa la arquitectura de conjunto de instrucciones (ISA) MIPS-III y gran parte de MIPS-IV, además de un conjunto de instrucciones personalizado desarrollado por Sony que operaba en grupos de 128 bits de ancho de 32 bits. enteros de 32 bits, 16 bits u 8 bits en forma de instrucción única y datos múltiples (SIMD) (es decir, se podrían sumar cuatro enteros de 32 bits a otros cuatro usando una sola instrucción). Las instrucciones definidas incluyen: sumar, restar, multiplicar, dividir, mín/máx, desplazamiento, lógica, recuento de ceros iniciales, carga/almacenamiento de 128 bits y desplazamiento de embudo de 256 bits a 128 bits, además de algunas no descritas por Sony para razones competitivas. Contrariamente a algunas ideas erróneas, estas capacidades SIMD no equivalían a que el procesador fuera de "128 bits", ya que ni las direcciones de memoria ni los números enteros en sí eran de 128 bits, sólo los registros SIMD/enteros compartidos. A modo de comparación, los registros de 128 bits de ancho y las instrucciones SIMD habían estado presentes en la arquitectura x86 de 32 bits desde 1999, con la introducción de SSE . Sin embargo, las rutas de datos internas tenían un ancho de 128 bits y sus procesadores eran capaces de operar en cantidades de 4x32 bits en paralelo en registros únicos.

Tiene una tubería entera de 6 etapas y una tubería de punto flotante (FP) de 15 etapas . Su variedad de registros consta de 32 registros VLIW SIMD de 128 bits (nombramiento/cambio de nombre), un acumulador de 64 bits y dos registros de datos generales de 64 bits, 8 registros de función fija de 16 bits y 16 registros de controlador de 8 bits. El procesador también tiene dos unidades lógicas aritméticas (ALU) de enteros de 64 bits , una unidad de almacenamiento de carga (LSU) de 128 bits, una unidad de ejecución de sucursales (BXU) y un coprocesador de unidad de punto flotante (FPU) VU1 de 32 bits. (que actuó como controlador de sincronización para VPU0/VPU1) que contiene un núcleo de procesador base MIPS con 32 registros FP de 64 bits y 15 registros enteros de 32 bits. Las ALU son de 64 bits, con una FPU de 32 bits que no cumple con IEEE 754. El conjunto de instrucciones personalizado 107 MMI (Extensiones multimedia) se implementó agrupando las dos ALU enteras de 64 bits. Tanto el canal de números enteros como el de punto flotante tienen seis etapas de longitud.

Para alimentar las unidades de ejecución con instrucciones y datos, hay un caché de instrucciones asociativo de conjunto bidireccional de 16 KB, un caché de datos asociativo de conjunto bidireccional sin bloqueo de 8 KB [4] y una RAM de bloc de notas de 16 KB . Tanto las cachés de instrucciones como de datos están virtualmente indexadas y etiquetadas físicamente, mientras que la RAM del scratchpad existe en un espacio de memoria separado. Se proporciona un buffer combinado de 48 instrucciones de doble entrada y traducción de datos para traducir direcciones virtuales . La predicción de bifurcaciones se logra mediante una caché de direcciones de destino de bifurcaciones de 64 entradas y una tabla de historial de bifurcaciones que está integrada en la caché de instrucciones. La penalización por error de predicción de rama es de tres ciclos debido al corto proceso de seis etapas.

La mayor parte del rendimiento de punto flotante de Emotion Engine lo proporcionan dos unidades de procesamiento vectorial (VPU), denominadas VPU0 y VPU1. Estos eran esencialmente DSP diseñados para matemáticas 3D y los precursores de los canales de sombreado de vértices de hardware . Cada VPU cuenta con 32 registros SIMD vectoriales de 128 bits (que contienen datos vectoriales 4D), 16 registros de punto fijo de 16 bits, cuatro unidades de multiplicación y acumulación de punto flotante (FMAC), una unidad de división de punto flotante (FDIV) y una memoria de datos local. . La memoria de datos de VPU0 tiene un tamaño de 4 KB, mientras que VPU1 cuenta con una memoria de datos de 16 KB.

Para lograr un gran ancho de banda, la memoria de datos de la VPU está conectada directamente al GIF, y la unidad DMA puede leer ambas memorias de datos directamente . Una instrucción de vector único consta de cuatro valores de punto flotante de precisión simple de 32 bits que se distribuyen a las cuatro unidades FMAC de precisión simple (32 bits) para su procesamiento. Este esquema es similar a las extensiones SSEx de Intel.

Las unidades FMAC necesitan cuatro ciclos para ejecutar una instrucción, pero como las unidades tienen una canalización de seis etapas , tienen un rendimiento de una instrucción por ciclo. La unidad FDIV tiene una canalización de nueve etapas y puede ejecutar una instrucción cada siete ciclos.

La IPU permitió la decodificación de imágenes comprimidas MPEG-2 , lo que permitió la reproducción de DVD y juegos FMV . También permitió la cuantificación vectorial para datos de gráficos 2D. [5]

La unidad de administración de memoria, el controlador RDRAM y el controlador DMA manejan el acceso a la memoria dentro del sistema. [5]

Las comunicaciones entre el núcleo MIPS, las dos VPU, el GIF, el controlador de memoria y otras unidades se manejan mediante un bus de datos interno de 128 bits de ancho que funciona a la mitad de la frecuencia de reloj del Emotion Engine pero, para ofrecer un mayor ancho de banda, también hay un bus de 128 bits. Ruta dedicada de 128 bits entre la CPU y VPU0 y una ruta dedicada de 128 bits entre VPU1 y GIF. A 150 MHz, el bus de datos interno proporciona un ancho de banda teórico máximo de 2,4 GB/s.

La comunicación entre Emotion Engine y la RAM se produce a través de dos canales de DRDRAM (memoria de acceso aleatorio dinámico Direct Rambus) y el controlador de memoria , que interactúa con el bus de datos interno. Cada canal tiene 16 bits de ancho y funciona a 400 MHz DDR (doble velocidad de datos). Combinados, los dos canales de DRDRAM tienen un ancho de banda teórico máximo de 25,6 Gbit/s (3,2 GB/s), aproximadamente un 33% más de ancho de banda que el bus de datos interno. Debido a esto, el controlador de memoria almacena en buffer los datos enviados desde los canales DRDRAM para que la CPU pueda utilizar el ancho de banda adicional.

Emotion Engine interactúa directamente con el sintetizador de gráficos a través del GIF con un bus dedicado de 64 bits y 150 MHz que tiene un ancho de banda teórico máximo de 1,2 GB/s. [6]

Para proporcionar comunicaciones entre Emotion Engine y el procesador de entrada y salida (IOP), la interfaz de entrada y salida conecta un bus de entrada y salida de 32 bits de ancho y 37,5 MHz con un ancho de banda teórico máximo de 150 MB/s al bus de datos interno. La interfaz proporciona suficiente ancho de banda para el conector de extensión PCMCIA que se usó para el adaptador de red con interfaz P-ATA incorporada para un acceso a datos más rápido y funcionalidad en línea. Una ventaja del gran ancho de banda fue que se podía utilizar fácilmente para introducir extensiones de hardware como el adaptador de red con soporte IDE HDD integrado u otras extensiones para ampliar la funcionalidad y el ciclo de vida del producto, lo que puede verse como una ventaja competitiva. Sin embargo, en variantes más nuevas (como la edición delgada), la interfaz ofrecería mucho más ancho de banda que lo que requieren los dispositivos de entrada y salida de PlayStation, ya que se eliminó la compatibilidad con HDD y se abandonó el diseño del conector PCMCIA en favor de un diseño más delgado.

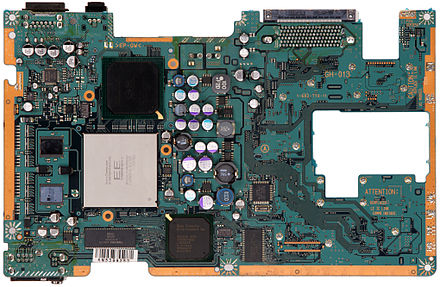

El Emotion Engine contenía 13,5 millones de transistores semiconductores de óxido metálico (MOS), [7] en un circuito integrado (IC) que medía 240 mm 2 . [8] Fue fabricado por Sony y Toshiba en un proceso de semiconductor de óxido metálico complementario ( CMOS ) de 0,25 µm ( 0,18 µm efectivo LG ) con cuatro niveles de interconexión.

El Emotion Engine estaba empaquetado en una matriz de rejilla de bolas de plástico (PBGA) de 540 contactos .

El uso principal de Emotion Engine era servir como CPU de PlayStation 2 . Los primeros SKU de PlayStation 3 también incluían un Emotion Engine en la placa base para lograr compatibilidad con los juegos de PlayStation 2. Sin embargo, la segunda revisión de PlayStation 3 carecía de un Emotion Engine físico para reducir costos, realizando todas sus funciones utilizando la emulación de software realizada por el procesador Cell Broadband , junto con un sintetizador de gráficos de hardware aún presente para lograr la compatibilidad con versiones anteriores de PlayStation 2. En todas las revisiones posteriores, se eliminó el sintetizador de gráficos; sin embargo, hay disponible un emulador de software de PlayStation 2 en revisiones posteriores del software del sistema para usar con los títulos clásicos de PS2 de Sony disponibles para su compra en Sony Entertainment Network.

Emotion Engine también se utilizó en la grabadora de vídeo digital PSX , así como en los modelos de televisor HDTV Sony WEGA HVX (números de modelo KDE-xxxHVX/KDL-xxxHVX) y Sony BRAVIA KDL22PX300, todos los cuales utilizaban hardware PlayStation 2.