Los paquetes planos sin conductores , como los de cuatro planos sin conductores ( QFN ) y los de dos planos sin conductores ( DFN ), conectan física y eléctricamente los circuitos integrados a las placas de circuitos impresos . Los paquetes planos sin conductores, también conocidos como micro leadframe (MLF) y SON (small-outline sin conductores), son una tecnología de montaje superficial , una de varias tecnologías de paquetes que conectan los circuitos integrados a las superficies de las placas de circuito impreso sin orificios pasantes . El plano sin conductores es un paquete encapsulado de plástico a escala de chip hecho con un sustrato de marco de conductores de cobre plano . Las pistas perimetrales en la parte inferior del paquete proporcionan conexiones eléctricas a la placa de circuito impreso . [1] Los paquetes planos sin conductores generalmente, pero no siempre, incluyen una almohadilla conductora térmica expuesta para mejorar la transferencia de calor fuera del circuito integrado (hacia la placa de circuito impreso). La transferencia de calor se puede facilitar aún más mediante vías metálicas en la almohadilla térmica. [2] El paquete QFN es similar al paquete de cuatro planos (QFP) y a una matriz de rejilla de bolas (BGA).

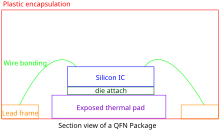

La figura muestra la sección transversal de un paquete plano sin plomo con un marco de conductores y unión de cables . Hay dos tipos de diseños de cuerpo, singulación por punzonado y singulación por sierra . [3] La singulación por sierra corta un gran conjunto de paquetes en partes. En la singulación por punzonado, se moldea un solo paquete en forma. La sección transversal muestra un cuerpo singulado por sierra con una almohadilla térmica adjunta. El marco de conductores está hecho de aleación de cobre y se utiliza un adhesivo conductor térmico para unir la matriz de silicio a la almohadilla térmica. La matriz de silicio está conectada eléctricamente al marco de conductores mediante cables de oro de 1 a 2 milésimas de diámetro .

Las almohadillas de un paquete con sierra individual pueden estar completamente debajo del paquete o pueden doblarse alrededor del borde del paquete.

Hay dos tipos de paquetes QFN comunes: QFN con cavidad de aire , con una cavidad de aire diseñada dentro del paquete, y QFN moldeados en plástico con el aire en el paquete minimizado.

Los QFN moldeados en plástico, que son menos costosos, suelen estar limitados a aplicaciones de hasta ~2–3 GHz. Suelen estar compuestos de solo 2 partes, un compuesto de plástico y un marco de conductores de cobre, y no vienen con tapa.

Por el contrario, el QFN con cavidad de aire suele estar formado por tres partes: un marco conductor de cobre, un cuerpo moldeado en plástico (abierto y no sellado) y una tapa de cerámica o plástico. Suele ser más caro debido a su construcción y se puede utilizar para aplicaciones de microondas de hasta 20–25 GHz.

Los paquetes QFN pueden tener una sola fila de contactos o una fila doble de contactos.

Este paquete ofrece una variedad de beneficios, entre ellos, una inductancia de cable reducida, un tamaño reducido "casi a escala de chip", un perfil delgado y un peso reducido. También utiliza almohadillas de E/S perimetrales para facilitar el enrutamiento de las pistas de PCB, y la tecnología de almohadilla de cobre expuesta ofrece un buen rendimiento térmico y eléctrico. Estas características hacen que el QFN sea una opción ideal para muchas aplicaciones nuevas en las que el tamaño, el peso y el rendimiento térmico y eléctrico son importantes.

Las tecnologías de empaquetado mejoradas y la miniaturización de los componentes pueden generar a menudo problemas nuevos o inesperados de diseño, fabricación y confiabilidad. Este ha sido el caso de los paquetes QFN, especialmente cuando se trata de su adopción por parte de nuevos fabricantes de equipos originales (OEM) de productos electrónicos que no son de consumo .

Algunas consideraciones clave para el diseño de QFN son el diseño de almohadillas y esténciles. Cuando se trata del diseño de almohadillas de unión, se pueden adoptar dos enfoques: definido por máscara de soldadura (SMD) o definido por no máscara de soldadura (NSMD). Un enfoque NSMD generalmente conduce a uniones más confiables, ya que la soldadura puede unirse tanto a la parte superior como a los lados de la almohadilla de cobre. [4] El proceso de grabado de cobre también suele tener un control más estricto que el proceso de enmascaramiento de soldadura, lo que da como resultado uniones más consistentes. [5] Esto tiene el potencial de afectar el rendimiento térmico y eléctrico de las uniones, por lo que puede ser útil consultar al fabricante del paquete para conocer los parámetros de rendimiento óptimos. Las almohadillas SMD se pueden utilizar para reducir las posibilidades de puentes de soldadura , sin embargo, esto puede afectar la confiabilidad general de las uniones. El diseño de la plantilla es otro parámetro clave en el proceso de diseño de QFN. El diseño de apertura adecuado y el grosor de la plantilla pueden ayudar a producir uniones más consistentes (es decir, mínimos huecos, desgasificación y piezas flotantes) con el grosor adecuado, lo que conduce a una mayor confiabilidad. [6]

También existen problemas en el lado de la fabricación. Para los componentes QFN más grandes, la absorción de humedad durante el reflujo de soldadura puede ser un problema. Si hay una gran cantidad de absorción de humedad en el paquete, entonces el calentamiento durante el reflujo puede provocar una deformación excesiva del componente. Esto a menudo da como resultado que las esquinas del componente se levanten de la placa de circuito impreso , lo que provoca una formación incorrecta de la unión. Para reducir el riesgo de problemas de deformación durante el reflujo, se recomienda un nivel de sensibilidad a la humedad de 3 o superior. [7] Varios otros problemas con la fabricación de QFN incluyen: flotación de la pieza debido al exceso de pasta de soldadura debajo de la almohadilla térmica central, gran vacío de soldadura, características deficientes de retrabajo y optimización del perfil de reflujo de soldadura. [8]

El empaquetado de componentes suele estar impulsado por el mercado de la electrónica de consumo, y se presta menos atención a las industrias de mayor confiabilidad, como la automotriz y la aviación. Por lo tanto, puede ser un desafío integrar familias de paquetes de componentes, como QFN, en entornos de alta confiabilidad. Se sabe que los componentes QFN son susceptibles a problemas de fatiga de soldadura , especialmente fatiga termomecánica debido al ciclo térmico . La separación significativamente menor en los paquetes QFN puede generar mayores tensiones termomecánicas debido al desajuste del coeficiente de expansión térmica (CTE) en comparación con los paquetes con cables. Por ejemplo, en condiciones de ciclo térmico acelerado entre -40 °C y 125 °C, varios componentes de paquete plano cuádruple (QFP) pueden durar más de 10 000 ciclos térmicos, mientras que los componentes QFN tienden a fallar en alrededor de 1000-3000 ciclos. [7]

Históricamente, las pruebas de confiabilidad han sido impulsadas principalmente por JEDEC , [9] [10] [11] [12] sin embargo, esto se ha centrado principalmente en las interconexiones de matriz y de primer nivel. IPC -9071A [13] intentó abordar esto centrándose en las interconexiones de segundo nivel (es decir, el encapsulado al sustrato de PCB). El desafío con este estándar es que ha sido más adoptado por los OEM que por los fabricantes de componentes, quienes tienden a verlo como un problema específico de la aplicación. Como resultado, ha habido muchas pruebas experimentales y análisis de elementos finitos en varias variantes de encapsulado QFN para caracterizar su confiabilidad y comportamiento de fatiga de soldadura . [14] [15] [16] [17] [18] [19] [20]

Serebreni et al. [21] propusieron un modelo semianalítico para evaluar la confiabilidad de las uniones soldadas QFN bajo ciclos térmicos. Este modelo genera propiedades mecánicas efectivas para el paquete QFN y calcula la tensión de corte y la deformación utilizando un modelo propuesto por Chen y Nelson. [22] Luego, la densidad de energía de deformación disipada se determina a partir de estos valores y se utiliza para predecir ciclos característicos hasta la falla utilizando una curva Weibull de 2 parámetros .

El encapsulado QFN es similar al encapsulado plano cuádruple , pero los cables no sobresalen de los lados del encapsulado. Por lo tanto, es difícil soldar a mano un encapsulado QFN, inspeccionar la calidad de las uniones soldadas o probar los cables.

Los distintos fabricantes utilizan distintos nombres para este encapsulado: ML (micro-leadframe) frente a FN (flat no-lead), además existen versiones con almohadillas en los cuatro lados (quad) y almohadillas en solo dos lados (dual), con un grosor que varía entre 0,9 y 1,0 mm para encapsulados normales y 0,4 mm para encapsulados extremadamente delgados. Las abreviaturas incluyen:

El encapsulado de microestructura de conductores (MLP) es una familia de encapsulados QFN de circuitos integrados , que se utiliza en diseños de circuitos electrónicos montados en superficie . Está disponible en 3 versiones que son MLPQ (Q significa cuádruple ), MLPM (M significa micro ) y MLPD (D significa doble ). Estos encapsulados generalmente tienen una almohadilla de sujeción de matriz expuesta para mejorar el rendimiento térmico. Este encapsulado es similar a los encapsulados a escala de chip (CSP) en cuanto a su construcción. Los MLPD están diseñados para proporcionar un reemplazo compatible con el tamaño de los encapsulados de circuitos integrados de contorno pequeño (SOIC).

El micro marco conductor (MLF) es un paquete encapsulado de plástico de tipo CSP con un sustrato de marco conductor de cobre. Este paquete utiliza pistas perimetrales en la parte inferior del paquete para proporcionar contacto eléctrico a la placa de circuito impreso . La paleta de unión de la matriz está expuesta en la parte inferior de la superficie del paquete para proporcionar una ruta de calor eficiente cuando se suelda directamente a la placa de circuito. Esto también permite una conexión a tierra estable mediante el uso de uniones descendentes o mediante una conexión eléctrica a través de un material conductor de unión de la matriz.

Una variación de diseño más reciente que permite conexiones de mayor densidad es el encapsulado de microconectores de doble fila (DRMLF). Se trata de un encapsulado MLF con dos filas de pistas para dispositivos que requieren hasta 164 E/S. Las aplicaciones típicas incluyen unidades de disco duro, controladores USB y LAN inalámbrica.

{{cite web}}: CS1 maint: copia archivada como título ( enlace )