La aceleración TLS (anteriormente conocida como aceleración SSL ) es un método para descargar el cifrado de clave pública que requiere un uso intensivo del procesador para Transport Layer Security (TLS) y su predecesor Secure Sockets Layer (SSL) [1] a un acelerador de hardware.

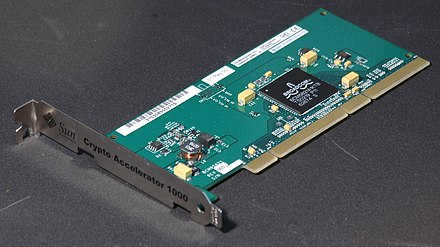

Normalmente, esto significa tener una tarjeta separada que se conecta a una ranura PCI en una computadora que contiene uno o más coprocesadores capaces de manejar gran parte del procesamiento SSL.

Los aceleradores TLS pueden utilizar CPU estándar , pero la mayoría utiliza chips ASIC y RISC personalizados para realizar la mayor parte del trabajo computacional difícil.

La parte más costosa en términos computacionales de una sesión TLS es el protocolo de enlace TLS, donde el servidor TLS (normalmente un servidor web) y el cliente TLS (normalmente un navegador web) acuerdan una serie de parámetros que establecen la seguridad de la conexión. Durante el protocolo de enlace TLS, el servidor y el cliente establecen claves de sesión (claves simétricas, utilizadas durante la duración de una sesión determinada), pero el cifrado y la firma de los mensajes del protocolo de enlace TLS se realizan mediante claves asimétricas, lo que requiere más potencia computacional que la criptografía simétrica utilizada para el cifrado/descifrado de los datos de la sesión.

Por lo general, un acelerador de hardware TLS descargará el procesamiento del protocolo de enlace TLS y dejará que el software del servidor procese la criptografía simétrica menos intensa del intercambio de datos TLS real , pero algunos aceleradores manejan todas las operaciones TLS y terminan la conexión TLS, por lo que el servidor solo ve las conexiones descifradas. A veces, los centros de datos emplean servidores dedicados para la aceleración TLS en una configuración de proxy inverso .

Las CPU x86 modernas admiten la codificación y decodificación del Estándar de cifrado avanzado (AES) en hardware, utilizando el conjunto de instrucciones AES propuesto por Intel en marzo de 2008.

Allwinner Technology ofrece un acelerador criptográfico de hardware en sus series de sistemas en chip ARM A10, A20, A30 y A80 , y todas las CPU ARM tienen aceleración en la arquitectura posterior ARMv8. El acelerador proporciona el algoritmo de clave pública RSA , varios algoritmos de clave simétrica ampliamente utilizados , funciones hash criptográficas y un generador de números pseudoaleatorios criptográficamente seguro . [2]