El Alpha 21164 , también conocido por su nombre clave, EV5 , es un microprocesador desarrollado y fabricado por Digital Equipment Corporation que implementó la arquitectura del conjunto de instrucciones Alpha (ISA). Se introdujo en enero de 1995, sucediendo al Alpha 21064A como microprocesador insignia de Digital. Fue sucedido por el Alpha 21264 en 1998.

El primer silicio del Alpha 21164 se produjo en febrero de 1994 y en él se iniciaron con éxito los sistemas operativos OpenVMS , Digital UNIX y Windows NT . Se probó a finales de 1994 y se introdujo en enero de 1995 a 266 MHz. En marzo de 1995 se introdujo una versión de 300 MHz. El 2 de octubre de 1995 se anunció el Alpha 21164 final, una versión de 333 MHz, disponible en cantidades de muestra. El Alpha 21164 fue reemplazado por el Alpha 21164A como microprocesador insignia de Digital en 1996, cuando una versión de 400 MHz estuvo disponible en grandes cantidades.

Digital utilizó el Alpha 21164 funcionando a varias frecuencias de reloj en sus servidores AlphaServer y estaciones de trabajo AlphaStation . Digital también utilizó el Alpha 21164 en sus computadoras de placa única Alpha VME 5/352 y Alpha VME 5/480 y en sus placas base AlphaPC 164 y AlphaPC 164LX . El socio de Alpha, Cray Research, utilizó un Alpha 21164 de 300 MHz en su supercomputadora T3E-600 . Terceros como DeskStation también construyeron estaciones de trabajo utilizando Alpha 21164.

El 21164 continuó el liderazgo en rendimiento desde el Alpha 21064A de 275 MHz hasta la introducción del Intel Pentium Pro en noviembre de 1995, cuando una versión de 200 MHz superó al 21164 de 300 MHz en el conjunto de pruebas SPECint95_base . El 21164 mantuvo su liderazgo en rendimiento de punto flotante. El 21164 de 333 MHz introducido el año siguiente superó al Pentium Pro, pero luego fue superado por el MIPS Technologies R10000 y luego por el Hewlett-Packard PA-8000 en el mismo año. [1]

El Alpha 21164 es un microprocesador superescalar de cuatro componentes capaz de emitir un máximo de cuatro instrucciones por ciclo de reloj a cuatro unidades de ejecución: dos enteras y dos de punto flotante . La canalización de números enteros tiene siete etapas de longitud y la canalización de punto flotante tiene diez etapas de longitud. El 21164 implementó una dirección virtual de 43 bits y una dirección física de 40 bits . Por tanto, era capaz de direccionar 8 TB de memoria virtual y 1 TB de memoria física .

La unidad de enteros constaba de dos canalizaciones de enteros y el archivo de registro de enteros . Las dos canalizaciones, la canalización de suma y la canalización de multiplicación, no son idénticas; cada una es responsable de ejecutar instrucciones diferentes, aunque ambas son capaces de ejecutar instrucciones comunes de suma, lógica, carga, comparación y movimiento condicional. La canalización de multiplicación ejecuta exclusivamente instrucciones de cambio, almacenamiento y multiplicación (en un multiplicador no canalizado). La canalización de adición ejecuta exclusivamente instrucciones de bifurcación.

A excepción de las instrucciones de bifurcación, movimiento condicional y multiplicación, todas las demás instrucciones comienzan y finalizan la ejecución durante la etapa cinco para una latencia de un ciclo. Las instrucciones de bifurcación y movimiento condicional se ejecutan durante la etapa seis para que puedan emitirse con una instrucción de comparación de cuyo resultado dependen.

El archivo de registro de enteros contenía cuarenta registros de 64 bits, de los cuales treinta y dos están especificados por Alpha Architecture y ocho son para uso de PALcode como memoria reutilizable. El archivo de registro tiene cuatro puertos de lectura y dos puertos de escritura divididos uniformemente entre las dos canalizaciones de enteros. [2]

La unidad de punto flotante constaba de dos canalizaciones de punto flotante y el archivo de registro de punto flotante. Las dos canalizaciones no son idénticas, una ejecutó todas las instrucciones de punto flotante excepto multiplicar y la otra ejecutó solo instrucciones de multiplicación. Ambos ductos tienen cuatro etapas. Un divisor de punto flotante no canalizado está conectado a la tubería de adición. Todas las instrucciones de punto flotante, excepto la de división, tienen una latencia de cuatro ciclos. Las divisiones tienen una latencia variable que depende de si la operación se realiza en números y números de punto flotante de precisión simple o doble. Incluyendo los gastos generales, las divisiones de precisión simple tienen una latencia de 15 a 31 ciclos, mientras que las divisiones de precisión doble tienen una latencia de 22 a 60 ciclos.

El 21164 tiene tres niveles de caché , dos integrados y uno externo y opcional. Los cachés y la lógica asociada constaban de 7,2 millones de transistores. [3]

El caché principal se divide en cachés separados para instrucciones y datos, denominados I-cache y D-cache respectivamente. Tienen un tamaño de 8 KB, están asignados directamente y tienen un tamaño de línea de caché de 32 bytes. El D-cache tiene dos puertos para mejorar el rendimiento y se implementa duplicando el caché dos veces. Utiliza una política de escritura directa y una política de asignación en lectura.

La caché secundaria, conocida como S-cache, está integrada y tiene una capacidad de 96 KB. Se requería un caché secundario integrado ya que el 21164 requería más ancho de banda del que podía proporcionar un caché secundario externo para proporcionarle suficientes instrucciones y datos. [4] El acceso al caché requirió dos ciclos debido a su gran área. Para mejorar el rendimiento, la caché está canalizada. Otro beneficio de un caché secundario integrado era que podía implementarse fácilmente como un caché multidireccional y, como resultado, el caché es asociativo de conjunto de tres vías , lo que ofrece mejores tasas de aciertos que los cachés de mapeo directo. [5] El S-cache, debido a la gran área física requerida, se implementó en dos mitades que flanquean la I-box, E-box, F-box y M-box. Esto se hizo para que el caché pudiera devolver datos en dos ciclos.

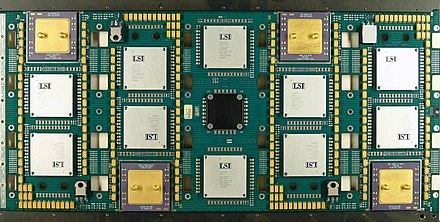

La caché terciaria, conocida como caché B, se implementa con SRAM externas. El caché B era opcional y algunos sistemas que usaban Alpha 21164 no tenían ninguno. El caché B podía tener una capacidad de 1 a 64 MB; las capacidades más pequeñas no eran compatibles porque el caché S integrado las inutilizaba. [6] Tiene mapeo directo, utiliza una política de escritura reescrita y una política de asignación en escritura. El B-cache está controlado por una lógica de interfaz externa integrada, a diferencia del 21064, que requería un controlador de caché externo. El B-cache podría construirse con SRAM asíncronas o síncronas. Se accede al caché B a través del bus del sistema.

La interfaz externa es un bus de sistema de 128 bits. El bus del sistema funciona a una frecuencia de reloj que es de 3 a 15 veces menor que la frecuencia del reloj interno, o de 20 a 100 MHz con una frecuencia de reloj interno de 300 MHz. La señal de reloj del bus del sistema es generada por el microprocesador.

La frecuencia del reloj interno se genera dividiendo una señal de reloj externo por dos. Por lo tanto, el Alpha 21164 requiere una señal de reloj externa de 600 MHz para un Alpha 21164 de 300 MHz.

El Alpha 21164 contiene 9,3 millones de transistores en una matriz de 16,5 por 18,1 mm (299 mm 2 ), lo que estaba cerca de los límites máximos del proceso. La matriz se fabricó en el proceso de semiconductores de óxido metálico complementario (CMOS) de quinta generación de Digital , CMOS-5, un proceso de 0,50 μm con cuatro niveles de interconexión de aluminio . [7] El 21164 utilizó una fuente de alimentación de 3,3 voltios (V). Disipó 46 W a 266 MHz, 51 W a 300 MHz, 56 W a 333 MHz.

El Alpha 21164 está empaquetado en una matriz de rejilla de pines intersticiales de cerámica (IPGA) de 499 pines que mide 57,40 por 57,40 mm. El paquete tenía un disipador de calor con dos pernos a los que se atornillaba el disipador de calor .

El Alpha 21164 fue la base de un desarrollo posterior con el nombre en código EV56 . Se presentó como Alpha 21164, pero originalmente se conocía como Alpha 21164A . Funcionó a frecuencias de reloj de 366, 433, 500, 533, 566, 600 y 666 MHz. [8] [9] [10]

Se describió por primera vez en octubre de 1995 en el Foro de Microprocesadores. El 13 de noviembre de 1995, Digital anunció que las muestras se enviarían a finales de mes. La primera versión, que funcionaba a 366 MHz, se introdujo en 1996. El 8 de julio de 1996, Digital anunció que estaba disponible una versión de 433 MHz y que se estaba probando una versión de 500 MHz con cantidades de volumen previstas para septiembre de 1996. La versión de 433 MHz tenía un precio de $1,492 por unidad en cantidades de 1,000. La versión de 600 MHz se introdujo el 31 de marzo de 1997 y se envió en grandes cantidades. Samsung Electronics firmó un acuerdo con Digital en junio de 1996 para adquirir el Alpha 21164A y la empresa fue la única en fabricar el modelo de 666 MHz. Las muestras de 366 a 500 MHz se introdujeron el 11 de noviembre de 1996 y el volumen estuvo disponible en 1997. El Alpha 21164A se fabricó en las plantas de fabricación de Digital en Hudson, Massachusetts y en Kihueng de Samsung, Corea del Sur .

Los usuarios de Alpha 21164A incluyeron Cray Research, Digital, Network Appliance (ahora NetApp) y DeskStation. Cray Research utilizó Alpha 21164A de 450, 600 y 675 MHz en modelos posteriores de su supercomputadora T3E . Digital utilizó el Alpha 21164A funcionando a varias frecuencias de reloj en sus AlphaServers , AlphaStations , estaciones de trabajo Celebris XL y estaciones de trabajo personales digitales . NetApp utilizó Alpha 21164A de 400, 500 y 600 MHz en sus sistemas de almacenamiento . DeskStation utilizó Alpha 21164A en sus estaciones de trabajo Raptor Reflex.

El cambio más notable fue la inclusión de Byte Word Extensions (BWX), una extensión de Alpha Architecture diseñada para mejorar el acceso a bytes y palabras. Estas instrucciones son ejecutadas por la canalización multiplicada. El Alpha 21164A contenía 9,66 millones de transistores en una matriz que medía 14,4 mm por 14,5 mm, para un área de matriz de 209 mm 2 . [11] Digital fabricó el troquel en su proceso CMOS de sexta generación, CMOS-6, un proceso de 0,35 μm con cuatro capas de interconexión. Samsung fabricó el troquel en su proceso de 0,35 μm con cuatro capas de interconexión basado en un proceso de 0,3 μm que desarrollaron a principios de 1996. El Alpha 21164A utilizó una fuente de alimentación de 3,3 V, disipando 31,0 W a 366 MHz, 36,0 W a 433 MHz, 41,0 W a 500 MHz, 43,5 W a 533 MHz y 48,5 W a 600 MHz.

El Alpha 21164PC , también conocido como PCA56 , es una versión de bajo costo del Alpha 21164A presentado el 17 de marzo de 1997. El microprocesador fue desarrollado conjuntamente por Digital y Mitsubishi Electric Corporation , y ambas compañías fabricaron el diseño. Posteriormente, Mitsubishi suspendió el acuerdo de desarrollo conjunto para futuros microprocesadores Alpha con Digital a principios de 1998 y dejó de fabricar el Alpha 21164PC a mediados de 1998, saliendo del mercado Alpha debido a las condiciones económicas en los mercados de la empresa. [12] [13]

El Alpha 21164PC operaba a frecuencias de reloj de 400, 466 y 533 MHz. Los cambios más importantes son la omisión del S-cache, un I-cache más grande y la inclusión de Motion Video Instrucciones (MVI), una extensión de Alpha Architecture que introdujo instrucciones de datos múltiples de instrucción única (SIMD) para mejorar el rendimiento de MPEG. codificación. Se eliminó el S-cache para reducir el número de transistores, lo que redujo el tamaño del chip y, a su vez, el costo. Se duplicó la capacidad del I-cache de 8 KB a 16 KB para compensar la falta de S-cache, ya que Alpha 21164 dependía del S-cache para complementar el I-cache a fin de proporcionar suficiente ancho de banda para lograr un rendimiento adecuado. . La cantidad de caché B se limitó a 512 KB a 4 MB, y también se admiten capacidades de 1 y 2 MB. El microprocesador utiliza una dirección virtual de 43 bits y una dirección física de 33 bits.

El Alpha 21164PC contenía 3,5 millones de transistores en una matriz que medía 8,65 por 16,28 mm, para un área de matriz de 141 mm 2 . Digital fabricó el troquel en el mismo proceso que el Alpha 21164, CMOS-5. El Alpha 21164PC estaba empaquetado en IPGA de 413 pines que medía 49,78 por 49,78 mm. Utilizaba una fuente de alimentación de 3,3 V, que disipaba 26,5 W a 400 MHz, 30,5 W a 466 MHz y 35,0 W a 533 MHz.

Digital utilizó la Alpha 21164PC en su placa base AlphaPC 164SX.

Un derivado del PCA56, el PCA57 fue diseñado y fabricado por Samsung Electronics en un proceso CMOS de 0,28 μm. El PCA57 se introdujo a finales de 1998 y funcionaba a frecuencias de reloj de 533, 600 y 666 MHz. Las mejoras a la microarquitectura PCA56 incluyeron capacidades duplicadas de I-cache y D-cache: 32 KB y 16 KB respectivamente. El PCA57 contenía 5,7 millones de transistores en una matriz que medía 6,7 mm por 15 mm, para un área de matriz de 101 mm 2 . Funcionó con una fuente de alimentación de 2,5 V y disipó 18 W a 533 MHz, 20 W a 600 MHz y 23 W a 666 MHz.

Digital utilizó el PCA57 en su placa base AlphaPC 164RX.

Digital y VLSI Technology desarrollaron conjuntos de chips para el 21164 y sus derivados. Digital también desarrolló circuitos integrados de aplicaciones específicas (ASIC) personalizados para su uso en los modelos de gama alta de su familia AlphaServer , como AlphaServer 8200 y 8400.

El 21171, también conocido como Alcor, fue el primer chipset del 21164, presentado en enero de 1995 junto con el microprocesador que admite. Fue desarrollado y fabricado por Digital. El 21171 es un DECchip 21071 actualizado y modificado para admitir el nuevo protocolo de bus del sistema que utiliza el 21164. Consistía en un chip de control que contenía la memoria y los controladores PCI, y cuatro chips de corte de datos que conectaban el bus de memoria de 256 bits y el bus PCI con el bus del sistema. El 21171 proporciona un bus PCI de 64 bits de ancho que funciona a 33 MHz.

El 21172, también conocido como Alcor2, era un 21171 actualizado que admitía el 21164A.

El chipset Pyxis, también conocido como 21174, admitía los microprocesadores 21164A y 21164PC. A diferencia de los conjuntos de chips anteriores, fue diseñado para sistemas de bajo costo. Como resultado, se trataba de un diseño de un solo chip empaquetado en una matriz de rejilla de bolas cerámicas (CBGA) de 474 contactos en lugar de paquetes múltiples. [14] Posteriormente se utilizó en aplicaciones sensibles al costo, como estaciones de trabajo de nivel básico ( Digital Personal Workstation a-Series ) y placas base como AlphaPC 164LX y 164SX. Cuando se presentó, el 21174 tenía un precio de 142 dólares estadounidenses en cantidades de 1.000 unidades. [15]

El 21174 contiene un controlador de memoria y un controlador PCI. El controlador de memoria admitía hasta 512 MB de memoria de acceso aleatorio dinámico síncrono (SDRAM) y accede a ella a través de un bus de memoria de 128 bits . La memoria puede ser ECC o protegida por paridad. El controlador PCI proporcionaba un bus PCI o PCI-X .

Polaris es un controlador de sistema desarrollado por VLSI Technology para computadoras personales que admite los microprocesadores 21164A y 21164PC. Polaris se anunció el 16 de junio de 1997. [16] Admite hasta 768 MB de EDO DRAM o hasta 512 MB de SDRAM. Se accede a la memoria a través de un bus de 128 bits. Proporciona un bus PCI de 32 bits y 33 MHz para E/S.

Los usuarios de Polaris incluyeron a Digital, por su placa base AlphaPC 164RX.