Un sistema multiprocesador se define como "un sistema con más de un procesador" y, más precisamente, "un número de unidades centrales de procesamiento conectadas entre sí para permitir que se realice un procesamiento paralelo". [1] [2] [3]

El objetivo principal de un multiprocesador es aumentar la velocidad de ejecución de un sistema. Los otros objetivos son la tolerancia a fallos y la adaptación a las aplicaciones. [4]

El término "multiprocesador" puede confundirse con el término " multiprocesamiento ". Mientras que el multiprocesamiento es un tipo de procesamiento en el que dos o más procesadores trabajan juntos para ejecutar múltiples programas simultáneamente, el multiprocesador se refiere a una arquitectura de hardware que permite el multiprocesamiento. [5]

Los sistemas multiprocesador se clasifican según cómo se maneja el acceso a la memoria del procesador y si los procesadores del sistema son de un solo tipo o de varios.

Existen muchos tipos de sistemas multiprocesador:

En los sistemas multiprocesadores acoplados de forma flexible, cada procesador tiene su propia memoria local, canales de entrada/salida (E/S) y sistema operativo . Los procesadores intercambian datos a través de una red de comunicación de alta velocidad enviando mensajes mediante una técnica conocida como " paso de mensajes ". Los sistemas multiprocesadores acoplados de forma flexible también se conocen como sistemas de memoria distribuida, ya que los procesadores no comparten memoria física y tienen canales de E/S individuales.

Sistema multiprocesador con una memoria compartida estrechamente conectada a los procesadores.

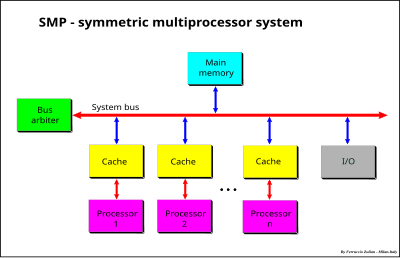

Un sistema multiprocesamiento simétrico es un sistema con memoria compartida centralizada llamada memoria principal (MM) que opera bajo un solo sistema operativo con dos o más procesadores homogéneos.

Hay dos tipos de sistemas:

Un sistema de multiprocesamiento heterogéneo contiene múltiples unidades de procesamiento, pero no homogéneas: unidades centrales de procesamiento (CPU), unidades de procesamiento gráfico (GPU), procesadores de señales digitales (DSP) o cualquier tipo de circuitos integrados específicos de la aplicación (ASIC). La arquitectura del sistema permite que cualquier acelerador (por ejemplo, un procesador gráfico) funcione al mismo nivel de procesamiento que la CPU del sistema.

Sistemas que funcionan bajo un único SO ( sistema operativo ) con dos o más procesadores homogéneos y con una memoria principal compartida centralizada.

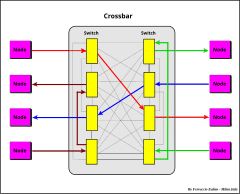

Un sistema multiprocesador simétrico (SMP) es un sistema con un conjunto de procesadores homogéneos que funcionan bajo un único sistema operativo con una memoria principal compartida y centralizada. Cada procesador, que ejecuta distintos programas y trabaja con distintos conjuntos de datos, tiene la capacidad de compartir recursos comunes (memoria, dispositivo de E/S, sistema de interrupción, etc.) que están conectados mediante un bus de sistema, una barra transversal o una combinación de ambos, o un bus de direcciones y una barra transversal de datos.

Cada procesador tiene su propia memoria caché que actúa como puente entre el procesador y la memoria principal. La función de la caché es aliviar la necesidad de acceso a los datos de la memoria principal, reduciendo así el tráfico del bus del sistema.

El uso de memoria compartida permite un tiempo de acceso a la memoria (UMA) uniforme.

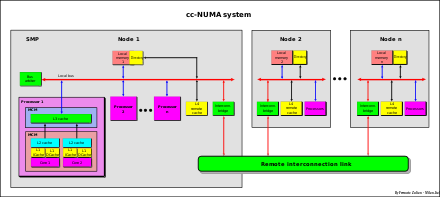

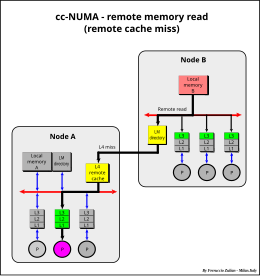

Se sabe que el sistema SMP tiene una escalabilidad limitada. Para superar esta limitación se suele utilizar la arquitectura denominada “cc-NUMA” (coherencia de caché – acceso a memoria no uniforme). La característica principal de un sistema cc-NUMA es tener memoria global compartida y distribuida a cada nodo, aunque el “acceso” efectivo que tiene un procesador a la memoria de un subsistema de un componente remoto, o “nodo”, es más lento en comparación con el acceso a memoria local, por lo que el acceso a memoria es “no uniforme”.

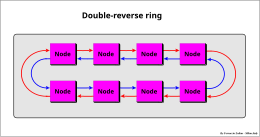

Un sistema cc–NUMA es un conjunto de sistemas SMP –cada uno llamado un "nodo", que puede tener un solo procesador, un procesador multi-núcleo, o una mezcla de los dos, de uno u otro tipo de arquitectura– conectados a través de una "red de conexión" de alta velocidad que puede ser un "enlace" que puede ser un anillo inverso simple o doble, o multi-anillo, conexiones punto a punto, [6] [7] o una mezcla de estos (por ejemplo, IBM Power Systems [6] [8] ), interconexión de bus (por ejemplo, NUMAq [9] ), "crossbar", "bus segmentado" ( NUMA Bull HN ISI ex Honeywell , [10] ), " enrutador de malla ", etc.

cc-NUMA también se denomina arquitectura de "memoria compartida distribuida" (DSM). [11]

La diferencia en los tiempos de acceso entre la memoria local y la remota también puede ser de un orden de magnitud, dependiendo del tipo de red de conexión utilizada (más rápida en interconexión de bus segmentado, de barra cruzada y punto a punto; más lenta en conexión de anillos seriales).

Para superar este límite, normalmente se utiliza una gran caché remota (consulte Caché remota ). Con esta solución, el sistema cc-NUMA se acerca mucho a un gran sistema SMP.

Ambas arquitecturas tienen desventajas que pueden resumirse de la siguiente manera:

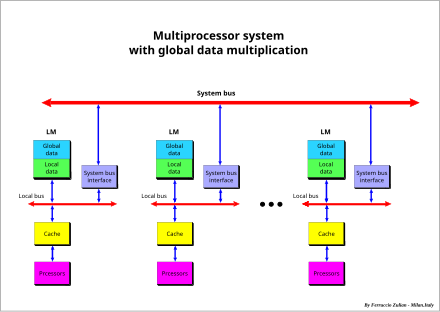

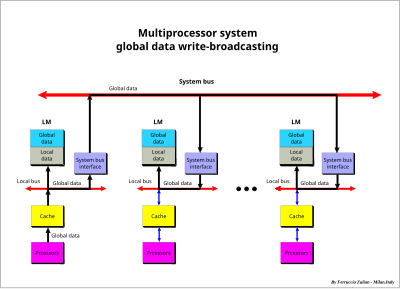

Un enfoque intermedio, entre los de las dos arquitecturas anteriores, es tener recursos comunes y recursos locales, como memorias locales (LM), en cada procesador.

Los recursos comunes son accesibles desde todos los procesadores a través del bus del sistema, mientras que los recursos locales sólo son accesibles para el procesador local. Las memorias caché pueden considerarse desde esta perspectiva como memorias locales.

Este sistema (patentado por F. Zulian [12] ), utilizado en el sistema basado en Unix DPX/2 300 (Bull Hn Information Systems Italia (ex Honeywell)), [13] [14] es una mezcla de sistemas acoplados de forma estrecha y flexible y hace uso de todos los avances de estas dos arquitecturas.

La memoria local se divide en dos sectores, datos globales (GD) y datos locales (LD).

El concepto básico de esta arquitectura es disponer de datos globales, es decir, información modificable, accesible a todos los procesadores. Esta información se duplica y se almacena en cada memoria local de cada procesador.

Cada vez que se modifican los datos globales en una memoria local, se envía una transmisión de escritura de hardware al bus del sistema hacia todas las demás memorias locales para mantener la coherencia de los datos globales. De este modo, los datos globales pueden ser leídos por cada procesador que acceda a su propia memoria local sin necesidad de que intervenga el bus del sistema. El acceso al bus del sistema solo es necesario cuando se modifican los datos globales en una memoria local para actualizar la copia de estos datos almacenada en las demás memorias locales.

Los datos locales se pueden intercambiar en un sistema débilmente acoplado mediante el paso de mensajes.