Los Intel 8253 y 8254 son temporizadores de intervalo programables (PIT), que realizan funciones de temporización y conteo utilizando tres contadores de 16 bits. [1]

La familia 825x fue diseñada principalmente para los procesadores Intel 8080/8085 , pero luego se utilizaron en sistemas compatibles con x86. Los chips 825x, o un circuito equivalente integrado en un chip más grande, se encuentran en todos los IBM PC compatibles y en computadoras soviéticas como la Vector-06C .

En los modelos compatibles con PC, el canal 0 del temporizador está asignado a IRQ -0 (la interrupción de hardware de mayor prioridad). El canal 1 del temporizador está asignado a la actualización de DRAM (al menos en los primeros modelos anteriores al 80386). El canal 2 del temporizador está asignado al altavoz de la PC .

La variante Intel 82c54 (c para lógica CMOS ) maneja señales de reloj de hasta 10 MHz. [1]

El 8253 se describe en la publicación "Catálogo de datos de componentes" de Intel de 1980. El 8254, descrito como un superconjunto del 8253 con índices de velocidad de reloj más altos, tiene una hoja de datos "preliminar" en el "Catálogo de datos de componentes" de Intel de 1982.

El 8254 está implementado en HMOS y tiene un comando "Read Back" no disponible en el 8253, y permite intercalar la lectura y escritura del mismo contador. [2]

Las PC modernas compatibles, ya sea cuando utilizan CPU SoC o southbridge, generalmente implementan compatibilidad total con 8254 para compatibilidad con versiones anteriores e interoperabilidad. [3] El comando Read Back es una característica de E/S vital para la interoperabilidad con CPU y GPU multinúcleo.

Existe una versión militar del Intel M8253 con un rango de temperatura de -55 °C a +125 °C que también tiene una tolerancia de potencia de ±10% de 5 V. [4] La versión CMOS 82C53 disponible fue subcontratada a Oki Electronic Industry Co., Ltd. [ 5] La versión de paquete disponible del Intel 82C54 estaba en PLCC de 28 pines de muestreo en el primer trimestre de 1986. [6]

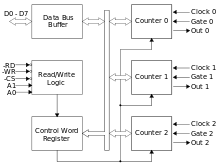

El temporizador tiene tres contadores, numerados del 0 al 2. [7] Cada canal puede programarse para funcionar en uno de seis modos. Una vez programados, los canales funcionan de forma independiente. [1]

Cada contador tiene dos pines de entrada: "CLK" ( entrada de reloj ) y "GATE", y un pin, "OUT", para la salida de datos. Los tres contadores son contadores descendentes de 16 bits independientes entre sí y pueden ser leídos fácilmente por la CPU . [8]

El modo de funcionamiento del PIT se modifica configurando las señales de hardware mencionadas anteriormente. Por ejemplo, para escribir en el registro de palabras de control, es necesario configurar CS = 0, RD = 1, WR = 0, A1 = A0 = 1.

Para inicializar los contadores, el microprocesador debe escribir una palabra de control (CW) en este registro. Esto se puede hacer configurando los valores adecuados para los pines del bloque de lógica de lectura/escritura y luego enviando la palabra de control al bloque de búfer de datos/bus.

El registro de palabras de control contiene 8 bits, etiquetados como D7...D0 (D7 es el MSB ). La decodificación es algo compleja. La mayoría de los valores establecen los parámetros para uno de los tres contadores:

Sin embargo, existen otras dos formas:

Al configurar el PIT, el microprocesador primero envía un mensaje de control y luego un mensaje de conteo al PIT. El proceso de conteo comenzará después de que el PIT haya recibido estos mensajes y, en algunos casos, si detecta el flanco ascendente de la señal de entrada GATE. Formato de byte de estado. El bit 7 permite que el software monitoree el estado actual del pin OUT. El bit 6 indica cuándo se puede leer el conteo; cuando este bit es 1, el elemento de conteo aún no se ha cargado y el procesador no puede volver a leerlo. Los bits 5 a 0 son los mismos que los últimos bits escritos en el registro de control.

Los bits D3, D2 y D1 de la palabra de control establecen el modo de funcionamiento del temporizador. Hay 6 modos en total; para los modos 2 y 3, se ignora el bit D3, por lo que los modos 6 y 7 que faltan son alias para los modos 2 y 3.

Todos los modos son sensibles a la entrada GATE, donde GATE alto provoca un funcionamiento normal, pero los efectos de GATE bajo dependen del modo:

El modo 0 se utiliza para generar un retardo de tiempo preciso bajo control de software. En este modo, el contador comenzará a contar desde el valor COUNT inicial cargado en él hasta 0. La velocidad de conteo es igual a la frecuencia de reloj de entrada.

El pin OUT se establece en bajo después de que se escribe la palabra de control y el conteo comienza un ciclo de reloj después de que se programa el conteo. OUT permanece en bajo hasta que el contador llega a 0, momento en el que OUT se establecerá en alto hasta que se vuelva a cargar el contador o se escriba la palabra de control. El contador vuelve a la 0xFFFFposición interna y continúa contando, pero el pin OUT nunca cambia nuevamente. La señal de la compuerta debe permanecer activa en alto para el conteo normal. Si la compuerta se pone en bajo, el conteo se suspende y se reanuda cuando se pone en alto nuevamente.

El primer byte del nuevo conteo, cuando se carga en el registro de conteo, detiene el conteo anterior.

En este modo, el 8253 se puede utilizar como multivibrador monoestable . La entrada GATE se utiliza como entrada de activación.

OUT estará inicialmente en nivel alto. OUT pasará a nivel bajo en el pulso de reloj después de un disparador para comenzar el pulso de un solo disparo y permanecerá en nivel bajo hasta que el contador llegue a cero. Luego, OUT pasará a nivel alto y permanecerá en nivel alto hasta el pulso CLK después del siguiente disparador.

Después de escribir la palabra de control y el conteo inicial, el contador se arma. Un disparador hace que se cargue el contador y se establezca OUT en un nivel bajo en el siguiente pulso CLK, iniciando así el pulso de un solo disparo. Un conteo inicial de N dará como resultado un pulso de un solo disparo con una duración de N ciclos CLK.

El pulso de un solo disparo se puede volver a disparar, por lo que OUT permanecerá bajo durante N pulsos CLK después de cualquier disparo. El pulso de un solo disparo se puede repetir sin tener que volver a escribir el mismo recuento en el contador. GATE no tiene ningún efecto en OUT. Si se escribe un nuevo recuento en el contador durante un pulso de un solo disparo, el pulso de un solo disparo actual no se ve afectado a menos que se vuelva a disparar el contador. En ese caso, el contador se carga con el nuevo recuento y el pulso de un solo disparo continúa hasta que el nuevo recuento expire.

En este modo, el dispositivo actúa como un contador de división por n, que se utiliza comúnmente para generar una interrupción de reloj en tiempo real.

Al igual que otros modos, el proceso de conteo comenzará el siguiente ciclo de reloj después de que se envíe COUNT. OUT permanecerá en nivel alto hasta que el contador llegue a 1 y se pondrá en nivel bajo durante un pulso de reloj. En el siguiente ciclo, el conteo se recarga, OUT se pone en nivel alto nuevamente y todo el proceso se repite.

El tiempo entre los pulsos altos depende del conteo preestablecido en el registro del contador y se calcula utilizando la siguiente fórmula:

Valor a cargar en el contador =

Tenga en cuenta que los valores en el registro COUNT varían de a 1; el registro nunca llega a cero.

Este modo es similar al modo 2. Sin embargo, la duración de los pulsos de reloj alto y bajo de la salida será diferente del modo 2.

Supongamos que el número se carga en el contador (el mensaje COUNT), la salida será alta para los conteos y baja para los conteos. Por lo tanto, el período será de conteos y, si es impar, el medio ciclo adicional se gasta con OUT alto.

Después de cargar la palabra de control y el contador COUNT, la salida permanecerá alta hasta que el contador llegue a cero. Luego, el contador generará un pulso bajo durante 1 ciclo de reloj (una señal estroboscópica); después de eso, la salida volverá a ser alta.

GATE bajo suspende el conteo, que se reanuda cuando GATE sube nuevamente.

Este modo es similar al modo 4. Sin embargo, el proceso de conteo se activa mediante la entrada GATE.

Después de recibir la palabra de control y el conteo, la salida se activará. Una vez que el dispositivo detecte un flanco ascendente en la entrada GATE, comenzará a contar. Cuando el contador llegue a 0, la salida se activará durante un ciclo de reloj; después, se activará nuevamente para repetir el ciclo en el siguiente flanco ascendente de GATE.

El 8253 se utilizó en los IBM PC compatibles desde su introducción en 1981. [9] En la actualidad, este PIT no se incluye como un chip independiente en un PC x86. En cambio, su funcionalidad se incluye como parte del puente sur del chipset de la placa base . En un chipset moderno, este cambio puede manifestarse en forma de un acceso notablemente más rápido a los registros del PIT en el espacio de direcciones de E/S x86 .

Todos los PC compatibles operan el PIT a una frecuencia de reloj de 105/88 = 1,193 18 MHz, 1 ⁄ 3 de la frecuencia de ráfaga de color NTSC que resulta de dividir el reloj del sistema (14,31818 MHz) por 12. Esto es un remanente de los primeros PC CGA : derivaban todas las frecuencias necesarias de un único cristal de cuarzo y, para hacer posible la salida de TV, este oscilador tenía que funcionar a un múltiplo de la frecuencia de subportadora de color NTSC. Esta frecuencia, dividida por 2 16 (el divisor más grande del que es capaz el 8253) produce la interrupción del temporizador de ≈18,2 Hz utilizada en MS-DOS y sistemas operativos relacionados.

En las IBM PC originales, el contador 0 se utiliza para generar una interrupción de cronometraje. El contador 1 se utiliza para activar la actualización de la memoria DRAM . El contador 2 se utiliza para generar tonos a través del altavoz de la PC .

Las placas base más nuevas incluyen contadores adicionales a través de la Interfaz avanzada de configuración y energía (ACPI), un contador en el Controlador local avanzado de interrupciones programables y un Temporizador de eventos de alta precisión . La propia CPU también proporciona la función Contador de sello de tiempo .

En las PC, la dirección del temporizador 0 (chip) está en el puerto 40h...43h y la del segundo temporizador 1 (chip) está en 50h...53h.

En las PC x86, muchas BIOS de tarjetas de video y BIOS de sistema reprogramarán el segundo contador para su propio uso. La reprogramación generalmente ocurre durante los cambios de modo de video, cuando se puede ejecutar la BIOS de video, y durante los cambios de estado de ahorro de energía y modo de administración del sistema, cuando se puede ejecutar la BIOS del sistema. Esto evita cualquier uso alternativo serio del segundo contador del temporizador en muchos sistemas x86.

Como se indicó anteriormente, el canal 0 se implementa como un contador. Por lo general, el valor inicial del contador se establece enviando bytes al puerto de control y luego a los registros del puerto de E/S de datos (el valor 36h se envía al puerto 43h, luego el byte bajo al puerto 40h y el puerto 40h nuevamente para el byte alto). El contador realiza una cuenta regresiva hasta cero y luego envía una interrupción de hardware (IRQ 0, INT 8) a la CPU . Luego, el contador se restablece a su valor inicial y comienza a contar nuevamente. La frecuencia de interrupción más rápida posible es un poco más de la mitad de un megahercio. La frecuencia más lenta posible, que también es la que normalmente usan las computadoras que ejecutan MS-DOS o sistemas operativos compatibles, es de aproximadamente 18,2 Hz. En estos sistemas operativos de modo real , el BIOS acumula la cantidad de llamadas INT 8 que recibe en la dirección de modo real 0040:006c, que puede ser leída por un programa.

A medida que un temporizador realiza una cuenta regresiva, su valor también se puede leer directamente leyendo su puerto de E/S dos veces , primero para el byte bajo y luego para el byte alto. Sin embargo, en aplicaciones de contadores de ejecución libre, como en la PC x86, es necesario escribir primero un comando de bloqueo para el canal deseado en el registro de control, de modo que ambos bytes leídos pertenezcan a un mismo valor.

Según un documento de Microsoft de 2002, "dado que las lecturas y escrituras desde este hardware [8254] requieren comunicación a través de un puerto de E/S, su programación requiere varios ciclos, lo que resulta prohibitivamente costoso para el sistema operativo. Por este motivo, la funcionalidad aperiódica no se utiliza en la práctica". [10]